FPGA到高速DRAM的接口設計(04-100)

——

讀數(shù)據(jù)到系統(tǒng)時鐘的再同步

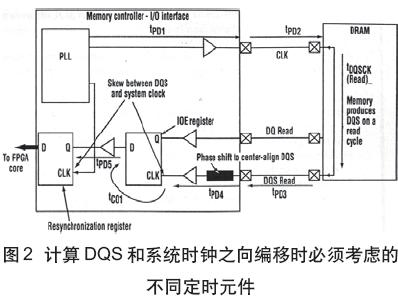

本文引用地址:http://www.104case.com/article/80852.htmDRAM接口設計的另一個問題是從DQS時鐘域到系統(tǒng)時鐘域變換讀數(shù)據(jù)。來自DRAM的讀數(shù)據(jù)首先在DQS時鐘域捕獲到存儲器控制器中。然后,此數(shù)據(jù)必須變化到系統(tǒng)時鐘域。為了保證正確地捕獲DQ信號在FPGA中,設計人員需要確定DQS和系統(tǒng)時鐘之間的偏移。

必須根據(jù)下列因素計算偏移精度來進行最小和最大定時分析(圖2):

·從PLL時鐘輸出到引腳的延遲(TpD1);

·時鐘板跡線長度延遲(TpD2);

·來自時鐘的DQS存取視窗(來自DDR存儲器數(shù)據(jù)表的TDQSCK)延遲。;

·DQS板跡線長度延遲(tpD3);

·在FPGA到I/O元件中來自DQS引腳的延遲(tpD4);

·I/O元件寄存器的微時鐘到輸出數(shù)時間延遲(tco1);

·從I/O寄存器到再同步寄存器的延遲(tpD5)。

評論