FPGA到高速DRAM的接口設計(04-100)

—— FPGA到高速DRAM的接口設計

FPGA做為系統(tǒng)的核心元件正在更多的用于網絡、通信、存儲和高性能計算應用中,在這些應用中都需要復雜的數(shù)據處理。

本文引用地址:http://www.104case.com/article/80852.htm所以,現(xiàn)在FPGA支持高速、外部存儲器接口是必須遵循的。現(xiàn)在的FPGA具有直接接口各種高速存儲器件的專門特性。本文集中描述高速DRAM到FPGA的接口設計。

設計高速外部存儲器接口不是一件簡單的任務。例如,同步DRAM已發(fā)展成高性能、高密度存儲器并正在用于主機中。最新的DRAM存儲器—DDR SDRAM,DDR2和RLDRAM II支持頻率范圍達到133MHz(260Mbits/s)~400MHz(800Mbits/s)。

因此,設計人員往往會遇到下列問題:DQ—DQS相位管理、嚴格的定時限制、信號完整性問題和同步開關轉換輸出(SSO)噪聲。另外一些板設計問題會延長設計周期或強迫接受降低性能。

DQ-DQS相位關系管理

DDR SDRAM靠數(shù)據選通信號(DQS)達到高速工作。DQS是用于DQ線上選通數(shù)據的非連續(xù)運行來保證它們彼此跟蹤溫度和電壓變化。DDR SDRAM 用片上鎖延遲環(huán)(DLL)輸出相對于相應DQ的DQS。

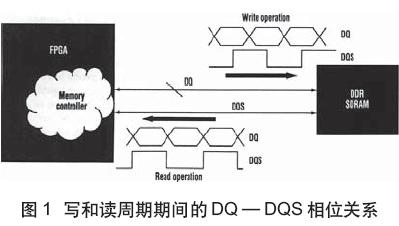

DQ和DQS信號間的相位關系對于DDR SDRAM和DDR2接口是重要的。當寫DRAM時,F(xiàn)PGA中的存儲器控制器必須產生一個DQS信號,此信號是中心對準在DQ數(shù)據信號中。在讀存儲器時,進入FPGA的DQS是相對于DQ信號的沿對準(圖1)。

評論