先進(jìn)封裝時(shí)代來臨 可望成市場差異化指標(biāo)

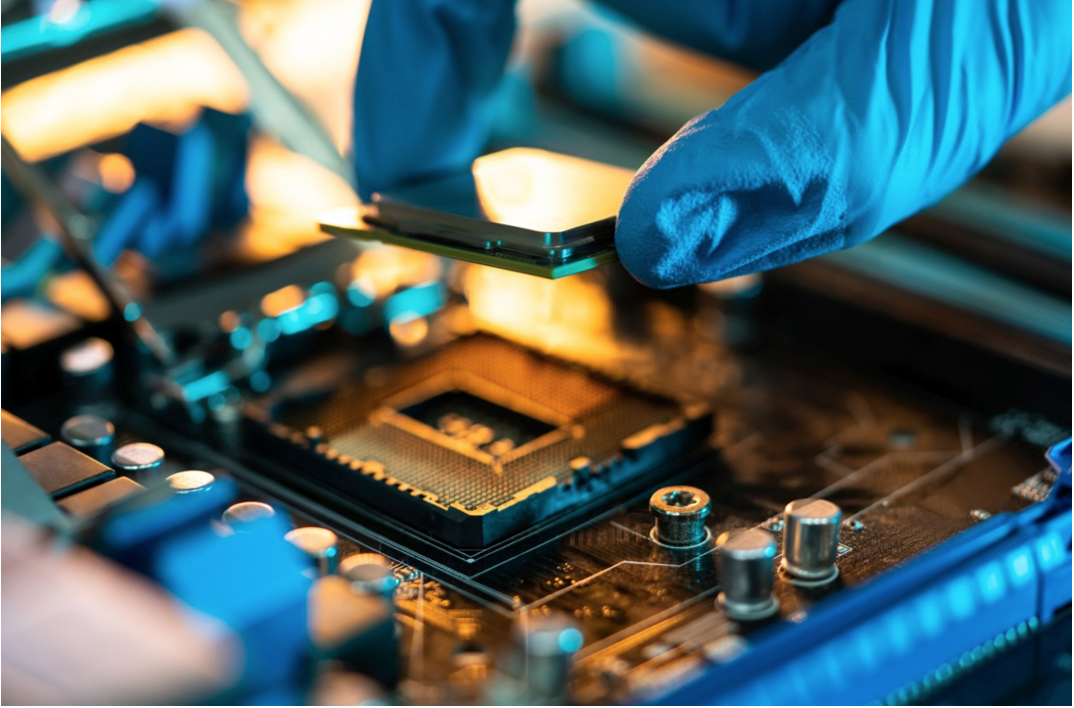

半導(dǎo)體封裝技術(shù)在過去不受重視,直到近期才被視為設(shè)計(jì)流程的關(guān)鍵之一,也是實(shí)現(xiàn)摩爾定律的關(guān)鍵。據(jù)Semiconductor Engineering網(wǎng)站報(bào)導(dǎo)指出,傳統(tǒng)上封裝幾乎不曾是設(shè)計(jì)架構(gòu)的主要部分,而關(guān)鍵指標(biāo)則往往是價(jià)格與耐用程度。

本文引用地址:http://www.104case.com/article/284873.htm然而,進(jìn)入28納米以下制程與物聯(lián)網(wǎng)(IoT)應(yīng)用當(dāng)中,封裝逐漸成為市場差異化指標(biāo),一改過去平面式矽元件設(shè)計(jì)與制程規(guī)則,封裝也成為從初始概念到設(shè)計(jì)到制備等每一道制程都得注意的層面。

Tirias Research分析師表示,半導(dǎo)體傳統(tǒng)三大中柱技術(shù)是微影制程(Lithography)、電晶體設(shè)計(jì)以及材料。然而,微影技術(shù)要實(shí)現(xiàn)摩爾定律愈來愈困難,而封裝技術(shù)涉及新式材料與處理技術(shù),晉升成第四大中柱。

半導(dǎo)體產(chǎn)業(yè)正從2D轉(zhuǎn)型3D技術(shù)制程,而系統(tǒng)級封裝(SiP)常是不可或缺的架構(gòu),飛思卡爾(Freescale)、英特爾(Intel)、邁威爾(Marvell)等芯片制造商也都相繼導(dǎo)入此架構(gòu)。

而部分市場的設(shè)計(jì)空間(Form Factor)受到功率預(yù)算(Power Budget)、封裝厚度、彈性等因素影響,系統(tǒng)級封裝已成必然趨勢。當(dāng)互連較厚、距離縮短、接線較少時(shí),功耗也將更低。

顧問機(jī)構(gòu)Yole Developpement報(bào)告指出,2015年是電子裝置的新世代,也是先進(jìn)封裝技術(shù)進(jìn)入量產(chǎn)與功能路線圖的初始年。先進(jìn)封裝可減少成本、提升效能、整合功能,且至2020年也可望占所有封裝服務(wù)44%、市值約300億美元。

智能型手機(jī)與平板電腦是先進(jìn)封裝的主要市場,而伺服器、PC、游戲平臺、電視、機(jī)上盒(set-top box)、穿戴式裝置、物聯(lián)網(wǎng)(IoT)等應(yīng)用也可望利用先進(jìn)封裝技術(shù)優(yōu)勢。

Lam Research產(chǎn)品執(zhí)行副總Richard Gottscho也表示,先進(jìn)封裝將形塑一可觀的市場,且刺激高深寬比(high-aspect ratio)介電層蝕刻(dielectric etch)、原子層沉積(ALD) 、矽穿孔(TSV)蝕刻等技術(shù)市場。

今 日封裝產(chǎn)業(yè)、商用芯片等已知導(dǎo)入扇出型(fan-out)、2.5D、單體式(Monolithic)3D等新式封裝技術(shù),然仍不是高度量產(chǎn)的市場,也尚 未發(fā)展出一套適合不同市場的標(biāo)準(zhǔn)制程經(jīng)驗(yàn)。而所有廠商爭相尋找最佳標(biāo)準(zhǔn)制程,也使得芯片、電路板、系統(tǒng)之間的區(qū)隔界線愈來愈模糊。

高效能運(yùn)算與網(wǎng)路業(yè)者eSilicon正開發(fā)2.5D芯片,而eSilicon表示,2015年需求倍增,以高頻寬存儲器(HBM)市場需求為主要驅(qū)動(dòng)力。目前, eSilicon面對的最大挑戰(zhàn)是中介板(Interposer)封裝成本與提升良率。

而芯片封裝技術(shù)也可交由其他公司處理,許多大型專業(yè)委外封裝測試(Outsourced Assembly and Test;OSAT)廠商也透過各式手段開發(fā)更先進(jìn)的納米技術(shù)與封裝技術(shù),包括購并先進(jìn)半導(dǎo)體制備器材等等。

同時(shí),臺積電、Global Foundries、三星電子(Samsung Electronics)、中芯國際、聯(lián)電等晶圓代工大廠也都忙升級先進(jìn)封裝技術(shù)。鴻海富士康、美商捷普集團(tuán)(Jabil)等電子制造公司也都正將觸手伸及印刷電路板(PCB)以外的領(lǐng)域。

而每家廠商采用的技術(shù)都有著不同的市場目的,舉例來說,適用于汽車市場的封裝技術(shù),將與適用消費(fèi)者市場的封裝技術(shù)大不同。

芯片的封裝方式,更會影響到芯片設(shè)計(jì)的其他層面,封裝內(nèi)部小小的變化就足以大幅改變封裝系統(tǒng)的電子或溫度特性。封裝內(nèi)部的材料有許多不同的拼裝方式,封裝內(nèi)的特殊應(yīng)用芯片(ASIC)、HBM、中介板以及封裝都有無限種組合方式,而重復(fù)使用的方式也有許多挑戰(zhàn)。

產(chǎn)業(yè)主要轉(zhuǎn)型趨勢從芯片層級拓展至系統(tǒng)層級,許多廠商正研發(fā)各式先進(jìn)封裝用的新式材料,包括有機(jī)中介板、復(fù)雜聚合物等等,以往不會被聯(lián)想在一起的公司也展開合作。

日月光與日本TDK在2015年宣布共同成立日月旸電子股份有限公司(ASE Embedded Electronics Incorporated),聯(lián)合目標(biāo)是生產(chǎn)內(nèi)嵌式基板,且在四層式塑膠基板內(nèi)將芯片微縮至50μm薄度。

單體式3D技術(shù)可望是最低成本的量產(chǎn)解決方案,不過,屆時(shí)也得考量TSV基板可鉆入多少個(gè)洞、鉆洞速度以及鉆洞密度。

英特爾、IBM等處理器業(yè)者以及像是賽靈思(Xilinx)等FPGA供應(yīng)商都將繼續(xù)追尋摩爾定律。目前為止,7納米制程已確認(rèn)在各家業(yè)者未來規(guī)劃藍(lán)圖當(dāng)中,而大家對5納米技術(shù)仍處觀望狀態(tài)。

制程微縮也愈來愈昂貴、耗時(shí),新式封裝技術(shù)則是提升效能、降低功耗、改善面積、添增功能與能力的替代方案。愈來愈多供應(yīng)鏈廠商也開始提供解決方案,可驅(qū)使半導(dǎo)體未來數(shù)十年朝此趨勢發(fā)展。

評論