借力英特爾專利技術 Altera第十代Stratix具備獨特優勢

觀察兩大可程式化邏輯元件供應商賽靈思(Xilinx)與Altera之間的較勁,就如同看蘋果(Apple)與三星(Samsung)之間的戰爭一般令人興奮;不過筆者并沒有要比較上述兩家公司,而是著重于他們嘗試將技術推向極限以保持市場競爭優勢的、令人屏息的熱忱。

本文引用地址:http://www.104case.com/article/277889.htmAltera在不久前才發表了第十代Stratix系列產品(參考閱讀:采用創新架構 Altera最新Stratix 10亮相);該公司所關注的設計挑戰與今日的各種關鍵應用相關,包括資料中心、物聯網(IoT)、400G/terabit網路、光學傳輸、5G無線通訊與8Kg訊。以資料中心為例,這類應用對更高的運算性能、靈活度與節能效益有越來越多需求;不過資料中心偏好使用商用伺服器,如此能更容易維護一個快速擴充的基礎設施。

物聯網是將各種智慧裝置相互連結在一起,以及與云端或是資料中心連結;這類應用需要高頻寬的基礎設施,好將資料中心處理分析過的資訊傳送到連網裝置上。因此,Altera認為這類具備最高成長潛力的應用領域,將會同時帶來為迎合以下需求必須克服的挑戰:不斷增加的功能、更高的頻寬與靈活度,以及最基本的小尺寸與更低耗電需求;當然還有最低成本。

所有這一切無法輕易地在電路板上實現,理由與不斷驅使我們實現更高整合度的原因是一樣的:PCB的尺寸大到無法達成我們渴望的功能性。再加上互連介面的頻寬限制,以及PCB走線的功率耗損,因此你有足夠的動機持續追求摩爾定律(Moore‘s Law)的預測。

Altera以更精細的14納米制程來因應以上挑戰,而對手Xilinx則是在最新Virtex、Kintex 與Zynq系列產品采用臺積電(TSMC)的16納米制程(發表時間在Altera的Stratix 10問世前不久);不過因為有各種IP區塊、嵌入式DRAM與快閃記憶體、影像感測器以及邏輯,成熟技術各自在不同的制程節點,積體(monolithic)解決方案已經不可行,所以兩家公司紛紛采用異質3D封裝技術。不過因為作法不同,在性能與成本方面也會有所不同。

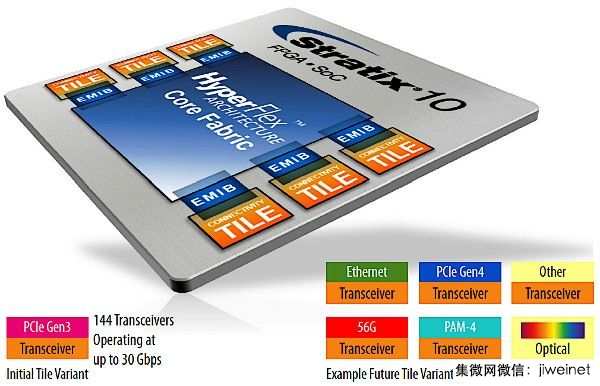

Altera的異質3D SiP技術將收發器裸晶(該公司稱之為Tile)與核心FPGA結構裸晶分開,因此收發器是位于核心結構旁邊,能以不同的制程節點來生產。

圖1: Altera的異質3D SiP技術將收發器Tile與核心FPGA結構裸晶分開

因此能以不同的制程節點來生產

最初的Stratix 10收發器Tile,包括PCIe Gen3 x16硬IP區塊;Altera表示,未來可能會推出其他硬體IP,例如PCIe Gen4、多埠乙太網路以及光收發器(更多Stratix 10相關資訊請參考此連結)。

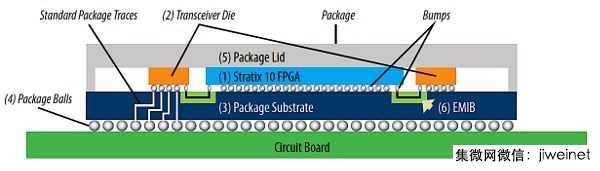

而Altera的解決方案與Xilinx產品最大的差異化,在于前者采用英特爾(Intel)專利的EMIB (Embedded Multi-die Interconnect Bridge)技術;EMIB是具備多繞線層(routing layer)的小型橋接晶片,可取代矽中介層(interposer)與矽穿孔(TSV)技術。

根據Intel與Altera的介紹,這種EMIB技術能降低訊號劣化與延遲的問題,因為裸晶不必透過中介層與TSV與封裝連結。

EMIB vs. 矽中介層-TSV

在一般晶片封裝中,矽中介層是一片比其他封裝中的互連裸晶尺寸更大的矽;而EMIB這種矽橋接(bridge)則是一小片嵌入兩片互連裸晶邊緣之下的矽,這能讓不同尺寸的裸晶在不同的地方連接,因此降低異質裸晶之間的物理限制

圖2: EMIB技術能減少對微凸塊的需求,因此降低制造的復雜度

在非EMIB解決方案中的大片矽中介層會(根據Altera說法是“過分地”)提高成本,而且容易出現像是變形曲翹的問題;EMIB也能降低對微凸塊數量的需求──傳統晶片會采用大量有微通孔的微凸塊,這提升了制造復雜度也會影響良率,當然也是提高成本的因素之一。對于不太可能取得EMIB技術的競爭隊史來說,Altera看來略勝一籌,不是嗎?

評論