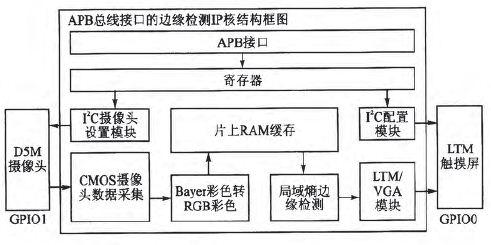

LEON3開源軟核處理器動態圖像邊緣檢測SoC設計

4.2動態圖像邊緣檢測SoC系統性能測試

本文引用地址:http://www.104case.com/article/273874.htm測試采用的硬件開發平臺為FPGA CycloneIIEP2C70F896C6N,Quartus II版本為10.0(32位),LEON3開發包版本為grlib-gp1-1.0.22-b4095.zip.D5M攝像頭工作在25MHz頻率,所采集的圖像分辨率為400×240,R、G、B每種色彩以10-bit二進制數據表示,D5M攝像頭每秒采集22~25幀圖像。LTM顯示屏的顯示分辨率為400×240,工作在33MHz頻率。

表3為測試得到的片上資源使用情況。從其結果可以分析得到,文中設計的動態圖像邊緣檢測SoC占據的片上資源在可以接受的范圍內。

且由實際測試可知,在外界環境適中的條件下,系統可以得到很好的圖像邊緣檢測效果。但由于圖像的分辨率較大,而邊緣檢測算法中所采用的窗口為3×3,相對于圖像來說較小,所以圖像上的一些小的陰影區域也會被檢測出來,形成陰影區域干擾,影響圖像的邊緣檢測效果。但總體來說,實現了動態圖像邊緣提取的最終目的。

結語

本文介紹了基于LEON3開源軟核處理器的動態圖像邊緣檢測SoC設計。

實驗結果表明該SoC系統工作正常,可以實現每秒22~25幀,最佳分辨率為400×240和640×480的動態圖像邊緣檢測功能,平均數據延時在70~80個系統時鐘。系統具有很好的可移植性與可配置性,占用資源少,速度快,具有廣泛的應用前景。

評論