突破委外產能限制 半導體OEM亟需重新整合供應鏈

Vardaman認為,邏輯元件和存儲器的單芯片整合最早將在2018年實現,但由于智慧型手機帶來的價格壓力,將使其難以在2019年以前采用3D TSV實現邏輯元件與邏輯元件的堆疊架構。

本文引用地址:http://www.104case.com/article/270726.htm“芯片堆疊正成為現實,AMD目前也在著手進行中,”AMD資深研究員Bryan Black觀察今天的2.5D和3D封裝解決方案表示,“但為什么現在才發生?”他聲稱AMD大約在十年前就已經解決了產能問題了,而且即將在其所有產品系列中使用TSV技術。

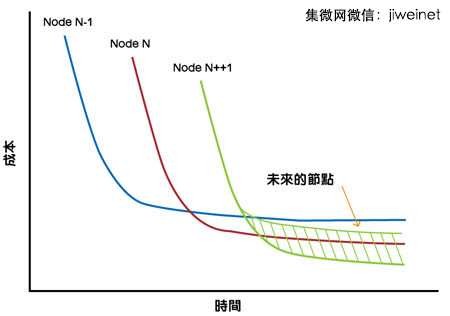

成本是首要原因,特別是以先進制程節點制造大型芯片時,由于產量減少,使得成本變得更高昂。“芯片整合也已經耗盡能量了,”Black認為,下一代制程節點的整體成本并不一定就會比較便宜。”

圖3:電晶體成本的不確定性

他的分析是,即使摩爾定律(Moore’s law)能夠為每個新制程節點帶來更多的電晶體,也不會是最適用的電晶體了,因為制程微縮將不再支援單一芯片上的不同功能,例如快速邏輯、低功耗邏輯、類比與快取等。

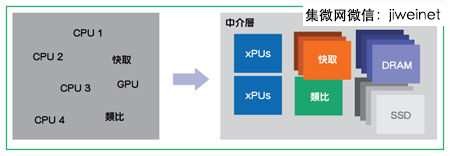

因此,從邏輯上來看,工程師將會試著把大型單芯片分成專用的元件,最大限度地發揮新的和現有制程節點的價值,而僅透過2.5D與3D堆疊進行重新整合。在他 看來,IC整合將永遠不會脫離中介層,相反地,矽中介層將會是未來的SoC關鍵介面,支援多種來源的3D元件,使其可依所需的步調擴展各種功能。

圖4:矽中介層將是未來的SoC介面。

隨著堆疊芯片的成本降低,OEM將能夠善加利用芯片共享以取代軟IP授權,購買市場上最好的芯片,并加以組裝制作成自有的SoC。為了自行整合,大型OEM將樂意投資于OSAT或進行封裝的代工廠。

“在服務器領域,還有誰比Google或Facebook更清楚他們需要的是什么?”Black指出,“這些公司并不希望被AMD或英特爾的硬體產品所束縛,但他們也不至于打造出更比半導體公司更多創新,他們只需要增加自己的創新就夠了。”

“因此,理想情況下,他們會希望市場上出現一款配備開放插槽的芯片,讓他們能創造自已想要的產品,”Black如此評論,同時也坦言曾經與Goolge的工程師交換過意見。

這種芯片級IP共享的愿景是:大型OEM可購買來自不同廠商經測試可用的芯片,以及管理自家的2.5D中介層插槽,在某些情況下甚至還可加入自家的ASIC于產品組合中,這一愿景與ATREG設想的垂直重新整合情景不謀而合。

“現在正是商業模式改變的有利時機!”Black的結語似乎暗示著芯片供應商更希望專注于銷售更多經IP驗證可用的分離式芯片,而非無法符合OEM期待的大型多功能整合芯片。

評論