基于SDRAM芯片立體封裝大容量的應用

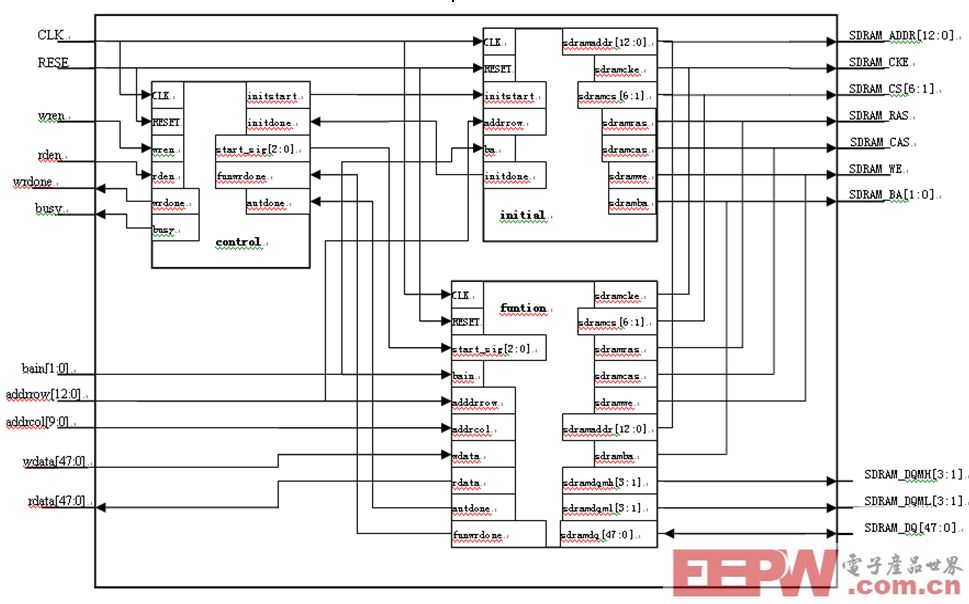

圖10控制器原理框圖

控制器分三部分:control邏輯控制、initial初始化和funtion功能部分。initial部分主要完成初始化模式設置;funtion部分主要完成刷新、讀和寫功能;control邏輯控制部分主要是控制協調initial初始化和funtion功能部分。

各個信號說明如表2所示:

表2 控制器信號說明

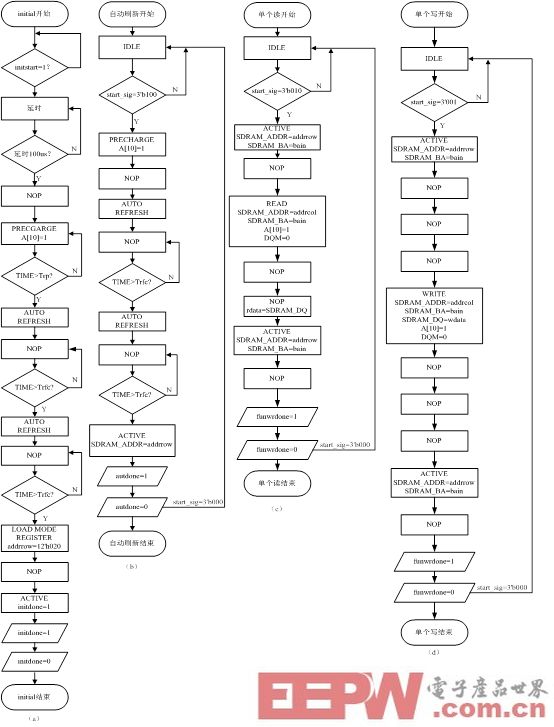

initial初始化

按照圖4初始化和模式設置時序圖,在初始化過程中,首先要延時100us,以便VCC和CLK穩定,接著發送NOP命令,再接著發PRECHARGE命令,此時發送A[10]=1,表示選擇所有banks。延時tRP時間后發送AUTO REFRESH和NOP命令,如果延時大于tRFC,那么再發AUTO REFRESH和NOP命令。延時tRFC時間后發LOAD MODE REGISTER命令,地址信號送入設置的模式數據,之后發NOP命令,最好發ACTIVE命令,并送入行地址和bank信號。操作如圖11(a)initial流程圖所示:

圖11(a)initial流程圖 圖11(b)自動刷新流程圖

圖11(c)單個讀流程圖 圖11(d)單個寫流程圖

自動刷新

按照圖7自動刷新時序圖,FPGA實現自動刷新可按照圖11(b)自動刷新流程圖來實現,共有十個狀態:IDLE、PRECHARGE、NOP、AUTO REFRESH、NOP、AUTO REFRESH、NOP、ACTIVE、autdone=1和autdone=0。這里并沒有把NOP、AUTO REFRESH合并是因為不想增加難度。另外,ACTIVE和autdone=1也可以放在同一個狀態中。自動刷新功能是由start_sig=3’b100發起的,之后就是按照十個狀態按順序進行。autdone=1和autdone=0兩個狀態在讀時序中并沒有出現,應用案例用著兩個狀態來產生一個正脈沖表示自動刷新動作完成了,用于各個部分協調。最后當start_sig=3’b000時返回IDLE狀態這個動作很重要,因為自動刷新、讀寫操作都是用同一個狀態變量,當刷新完成時狀態變量處于autdone=0這個狀態,假如刷新完成之后進行讀操作,那么最終只進行了autdone=0這步操作,而不是從IDLE到autdone=0一系列的操作。其他操作原理同樣如此

單個讀操作

按照圖9單個讀時序圖,FPGA實現讀操作可按圖11(c)單個讀流程圖來完成。實現共有十個狀態:IDLE、ACTIVE、NOP、READ、NOP、NOP 、ACTIVE、NOP 、autdone=1和autdone=0。單個讀功能由start_sig=3’b010發起的,之后就是按照十個狀態按順序進行。autdone=1和autdone=0兩個狀態產生一個正脈沖表示讀動作完成了。最后當start_sig=3’b000時返回IDLE狀態。

單個寫操作

按照圖8單個寫時序圖,FPGA實現寫操作可按圖11(d)單個寫流程圖來完成。實現共有十個狀態:IDLE、ACTIVE、NOP、NOP、NOP、WRITE、NOP、NOP 、NOP 、ACTIVE、NOP 、autdone=1和autdone=0。單個寫功能由start_sig=3’b001發起的,之后就是按照13個狀態按順序進行。autdone=1和autdone=0兩個狀態產生一個正脈沖表示寫動作完成了。最后當start_sig=3’b000時返回IDLE狀態。

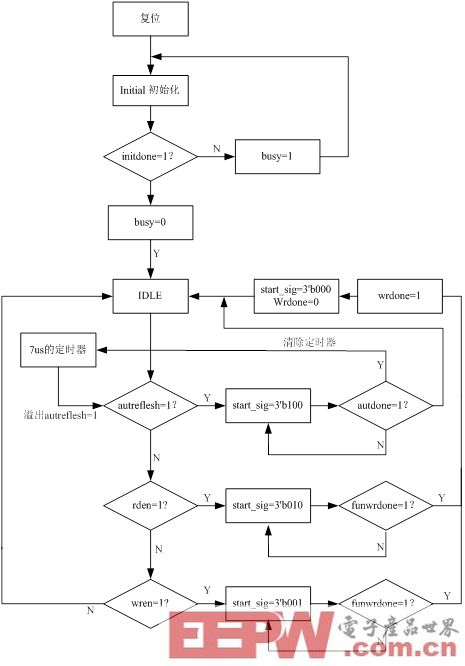

邏輯控制部分

邏輯控制部分是一個重要的部分,是整個控制器的控制中心。邏輯控制部分主要功能如圖12邏輯控制部分流程圖所示。

邏輯控制部分在上電復位時,首先要完成初始化模式設置,當初始化模塊完成初始化輸出initdone時,邏輯控制部分輸出busy=0,表示初始化完成了。接著進入空閑IDLE狀態,在這個狀態中進行刷新autreflesh、讀rden和寫wren的檢測。當檢測到autreflesh=1時,表示要進行刷新動作置start_sig=3’b100啟動刷新功能,刷新完成之后得到反饋信號autdone=1,之后清除定時器,置start_sig=3’b100讓功能模塊狀態變量回到空閑IDLE狀態,并且回到邏輯控制部分的空閑狀態。當檢測到rden=1時,置start_sig=3’b010啟動讀功能,等到funwrdone=1讀完成時,置start_sig=3’b000讓功能模塊狀態變量回到空閑IDLE狀態,并輸出一個wrdone的正脈沖表示讀功能完成,然后回到邏輯控制部分的空閑狀態。當檢測到wren=1時,置start_sig=3’b001啟動寫功能,等到funwrdone=1讀完成時,置start_sig=3’b000讓功能模塊狀態變量回到空閑IDLE狀態,并輸出一個wrdone的正脈沖表示寫功能完成,然后回到邏輯控制部分的空閑狀態。刷新讀寫功能的檢測是有順序的,也就是說是有優先級的,刷新比較重要,不立即數據就會丟失,所有首先檢測刷新動作,相對來說讀寫并沒有比較明顯的區別,本案例讀的優先級比寫的優先級高。

圖12 邏輯控制部分流程圖

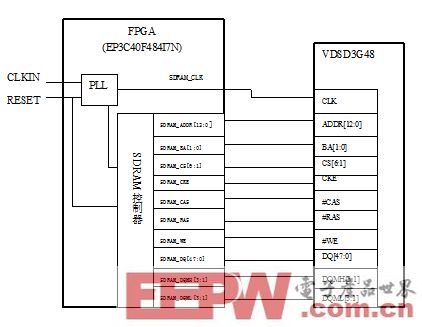

2、 FPGA與VDSD3G48的硬件連接

FPGA與VDSD3G48硬件連接圖

如圖所示,FPGA輸入CLKIN時鐘和RESET復位信號,其中復位信號能夠復位鎖相環PLL和SDRAM控制器,時鐘輸入經過PLL倍頻之后一路送給SDRAM控制器,另一路送給輸出送給VDSD3G48。FPGA的SDRAM_ADDR[12:0]、SDRAM_BA[1:0]、SDRAM_CS[6:1]、SDRAM_CKE、SDRAM_CAS、SDRAM_RAS、SDRAM_WE、SDRAM_DQ[47:0]、SDRAM_DQMH[3:0]、SDRAM_DQML[3:1]分別與VDSD3G48的ADDR[12:0]、BA[1:0]、CS[6:1]、CKE、#CAS、#RAS、#WE、DQ[47:0]、DQMH[3:1]和DQML[3:1]相連。

結 語

對于同步隨機動態存取存儲器(SDRAM)堆疊而成的立體封裝的大容量存儲芯片VDSD3G48,要進行初始化和刷新操作才能保證訪問的正確性。同時基于SDRAM芯片立體封裝存儲器縮短了內部信號連接長度、減少了寄生效應,增強了抗干擾能力,可廣泛用于車輛、衛星、飛機和空間站等領域。

存儲器相關文章:存儲器原理

評論