基于SOC的SPI接口設計與驗證

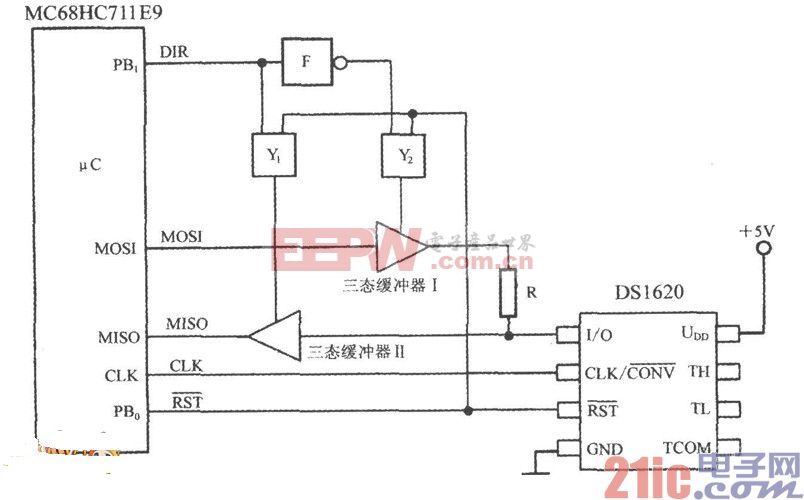

這部分設計作為SPI的從設備與主機進行數據交換,與spi_shift模塊時鐘同步。通信開始后,從機數據最高位開始串行輸入到MISO,主機發出的數據從最低位串行輸出到MOSI。

本文引用地址:http://www.104case.com/article/234922.htm3 SPI接口的功能仿真

本設計采用Verilog HDL編寫Testbench,使用ModelSim軟件進行功能仿真,并用Debussy軟件聯合調試并觀察波形。為了實現主從設備通信的仿真,編寫了一個p_master模塊并例化到測試代碼里面來模擬主機SoC對spi_master的操作,主要包括一個數據寫task、一個數據讀task、一個數據比較task。分別測試了1 b,8 b,16 b,32 b,64 b,128 b的數據。仿真全部通過,局部仿真波形如圖5所示。

以第一次傳輸為例進行分析,傳輸時調用寫任務,分別向寄存器DIVIDER、TX_0、CTRL寫入32’h01、32’h5a、32’h308,設定spi_sla ve.data為32’ha5967e5a。由波形看出,數據在ss[0]有效傳輸,傳輸完成后MIS0=8’b10100101(即32’ha5),MOSI=8’b01011010(即32’h5a),滿足了上升沿發送下降沿接收及高位先開始的數據傳輸時序。在100 MHz的主時鐘頻率下,得到串行時鐘頻率25 MHz,為4分頻,符合式(1)的計算。

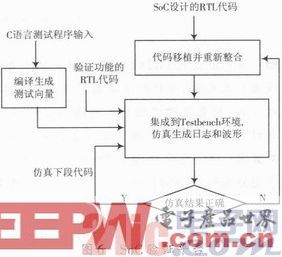

4 SPI接口的SoC平臺驗證

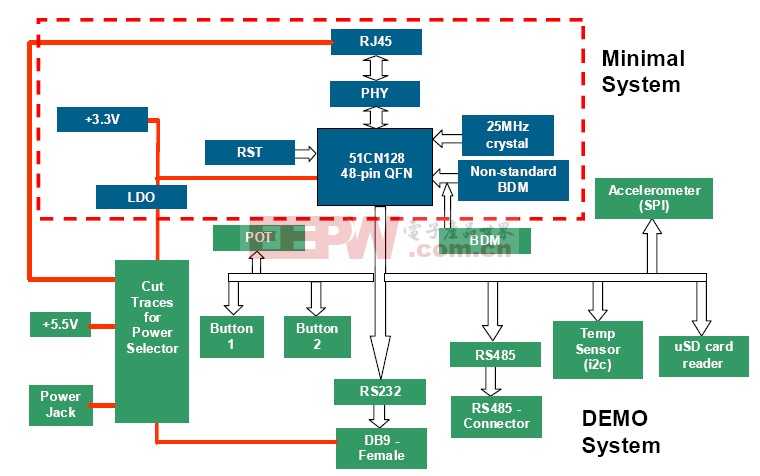

驗證用SoC平臺具有良好的可重用性和通用性,可以方便的掛接帶有AHB/APB總線接口的IP核,并通過內部寄存器對其進行配置和驗證,避免了對不同IP設計需要不同的Testbench平臺,提高了IP驗證的效率。本設計用到的SoC驗證平臺如圖6所示,驗證環境為Linux操作系統,仿真工具為VCS。

在SoC驗證平臺中,SPI接口作為外設連接在APB總線的Slave4端口上,地址空間為0xA400_0000~0XA4FF_FFFF。用C測試程序向Tx0寫32’h67,spi_slave.data=32’h0,局部仿真波形如圖7所示,MOSI=8’b01100111(即32’h67),MISO=8’b0,結果表明符合要求。

5 結語

本文實現了基于AMBA 2.0總線的、可作為IP核用于SoC設計的SPI接口的設計,并且經過全面的仿真驗證,可以看出本設計滿足性能要求。

評論