基于SOC的SPI接口設計與驗證

摘要:給出了一個可用于SoC設計的SPI接口IP核的RTL設計與功能仿真。采用AMBA 2.0總線標準來實現SPI接口在外部設備和內部系統之間進行通信,在數據傳輸部分,摒棄傳統的需要一個專門的移位傳輸寄存器實現串/并轉換的設計方法,采用復用寄存器的方法,把移位傳輸寄存器和發送寄存器結合在一起,提高了傳輸速度,也節約了硬件資源。采用SoC驗證平臺進行SoC環境下對IP的驗證,在100 MHz時鐘頻率下的仿真和驗證結果表明,SPI接口實現了數據傳輸,且滿足時序設計要求。

本文引用地址:http://www.104case.com/article/234922.htm0 引言

SPI(Serial Peripheral Interface)是一種同步串行總線接口,很多器件如E2PROM、FLASH、實時時鐘、A/D轉換器等都用到了SPI接口,它也是SoC中的一個常用外圍功能模塊。AMBA總線是由ARM公司開發的一種高性能、開放性SoC系統總線,它主要包括AHB,ASB和APB三種總線類型。AHB總線主要用于連接高性能、高速度的系統模塊,如CPU,DSP,SRAM等;APB總線主要用于連接低速外圍模塊,如UART,I2C等,接口簡單,效率高,功耗低;ASB總線通過連接系統高速部件來實現高速通信,一般較少用到。

本文設計一個可作為IP核用于SoC設計的SPI接口,采用AMBA2.0總線標準來實現SPI接口在外部設備和內部系統之間進行通信,SPI接口作為低速外圍模塊掛載在APB總線上。

1 SPI接口的定義

1.1 接口信號

SPI的接口信號為同步串行時鐘SCLK、主機輸入/從機輸出MISO、主機輸出/從機輸入MOSI、從機選擇

(低電平有效),由于只用到四根線工作,與其他接口相比具有結構簡單、速度快的優點。SPI有主/從兩種工作模式,SPI總線的串行時鐘SCLK用來同步數據傳輸,在主模式下由主機產生,從機選擇信號

用來決定外部設備是否被選作SPI的從設備。主從設備連接方式如圖1所示。

1.2 內部寄存器

SPI的內部寄存器如表1所示。

1.3 傳輸時序

在本設計中,SPI的傳輸時序由控制寄存器CTRL來決定。CTRL[9]定義為RX_NEGE,置1表示數據在時鐘下降沿接收,置0為上升沿接收;CTRL[10]定義為TX_NEGE,置1表示數據在下降沿發送,置0為上升沿發送;CTRL[11]定義為LSB,置1表示數據從最低位開始傳輸,置0從最高位開始傳輸。CTRL[6:0]定義為CHAR_LEN,為數據傳輸長度,最長可為128 b。以其中一種傳輸時序為例說明,如圖2所示。

2 SPI接口的RTL設計

本設計是針對SoC系統的,目標是實現適用于SoC設計并且符合SPI通信協議的IP核,實現SoC通過此SPI接口和外設通信。所以,本設計分成SPI主機模塊spi_master的設計和SPI從機模塊spi_slave的設計,采用Verilog HDL進行RTL設計。

2.1 spi_master模塊設計

spi_master的功能主要包括:

(1)實現主機通過APB總線初始化spi_master的寄存器;

(2)實現spi_master和spi_slave之間的數據交換。

因此,spi_master模塊主要就是實現分頻和串并轉換,主要包含時鐘產生子模塊spi_clgen和數據傳輸子模塊spi_shift,其設計結構如圖3所示。

2.1.1 時鐘產生子模塊設計

該子模塊主要作用是產生SPI主/從設備通信所需的同步串行時鐘sclk。在主模式下,sclk由系統提供的時鐘信號pclk分頻產生,產生的串行時鐘的時鐘頻率由式(1)計算得來:

傳輸開始前,cnt載人DIVIDER值,滿足傳輸條件下cnt減1計數,減為0時,輸出時鐘clk_out翻轉,并且在clk_out的上升沿和下降沿分別產生pos_edge和neg_edge信號。

2.1.2 數據傳輸子模塊設計

該子模塊的主要功能是完成數據的串/并轉換。在本設計中,該子模塊負責把內部APB總線并行傳輸進來的數據轉化成串行數據傳輸給SPI從設備,并且把外部SPI從設備串行傳輸進來的數據轉化成并行數據傳入到APB總線上。

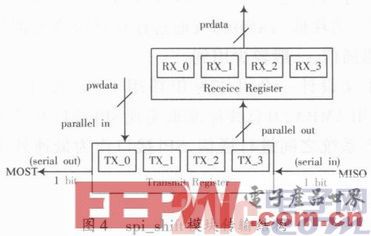

傳統的串/并轉換設計方法需要一個專門的移位傳輸寄存器,本設計采用了復用寄存器的方法,把移位傳輸寄存器和發送寄存器結合在一起。當傳輸停止且總線鎖存使能時,數據從APB總線并行傳輸到spi_shift移位傳輸寄存器即發送寄存器TxX,然后在傳輸時鐘使能情況下串行輸出到MOSI;而在主機接收使能的情況下,由從機MISO串行輸人數據至spi_shift移位傳輸寄存器。傳輸結構如圖4所示,從圖4可以看出,數據傳輸位寬最大可達128 b/s。

2.1.3 RTL代碼設計

spi_master模塊代碼設計劃分如下:

(1)寄存器選擇使能信號的地址譯碼電路;

(2)讀寄存器部分,將并行數據輸出到APB總線上;

(3)控制寄存器ctrl、時鐘分頻寄存器divider、從機選擇寄存器ss初始化部分;

(4)例化時鐘分頻子模塊和數據傳輸子模塊。

為了提高代碼的復用性,特別設計了一個宏定義模塊,主要定義了傳輸最大位數SPI_MAX_CHAR,分頻寄存器位數SPI_DIVIDER_LEN,從機選擇數目SPI_SS_NB等相關數據。

2.2 spi_slave模塊設計

評論