基于FPGA的DDR內存條的控制研究與設計

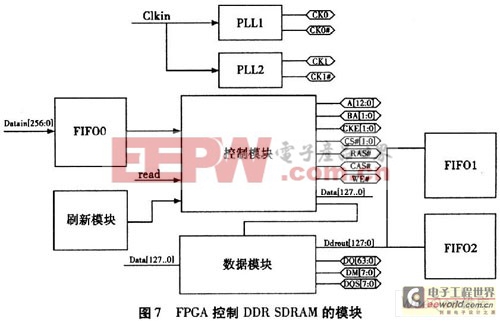

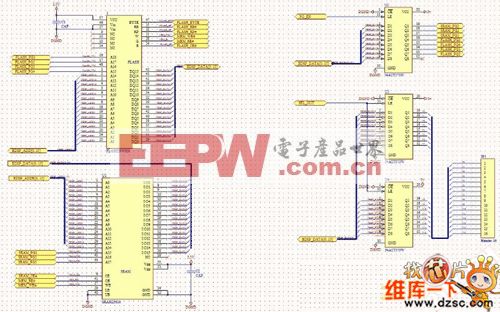

本設計中使用的FPGA是ALTERA公司的cyclone II系列的EP2C20F484C6。對內存條的工作模式設置為BL=4,CL=3,如圖7為FPGA對DDR SD-RAM的控制模塊框圖。

其中,Clkin為外部輸入的時鐘信號,為了使FPGA到DDR SDRAM的兩對時鐘信號的質量盡量好,使用FPGA內部的兩個鎖相環輸出差分時鐘信號。為了保證鎖相環輸出的兩路差分信號相位一致,在設計PCB時我們使晶振輸出到FPGA兩個PLL輸入的布線距離相等,為了保證兩個鎖相環輸出信號到達DDR SDRAM接口時相位一致,由FPGA鎖相環輸出到DDR SDRAM的接口布線長度相等。

控制模塊采用的工作模式是按照圖2所示的狀態來跳轉,上電以后首先是對DDR SDRAM進行初始化,初始化完成以后就可以進出等待工作的狀態。此時刷新計數器開始計數,等待7.8 us后給出刷新請求,在空閑狀態時(IDEL)刷新請求的優先級最高,響應刷新請求后執行REFR-ESH指令同時復位刷新計數器。初始化后如果FIF00的讀空標志為O說明FIF00中有數據,此時可以進入到寫狀態。由于采用的是BL=4的工作狀態,寫操作每次都寫入4個64位的數。所以,我們將輸入的數據進行并位成256位的數,每次寫操作只需要從FIF00中讀出一個256位的數。假設我們采用1OOMHz的時鐘,每寫4個64位的數大概需要10個時鐘周期。如果輸入的數據位寬為16位,那么由外部傳給FPGA的數據率要小于160 MHz。寫操作完成的時候進入空閑狀態,等待刷新標志或者讀空標志。讀的時候需要等待系統發出讀命令(read),然后進入讀狀態,讀出的數據由Ddrout[127:O]送到FIF01和FIF02中。通過控制FIF01和FIF02的寫請求信號來實現將數據分別寫入。讀的時候BL=4每次讀出4個64位數,執行一次讀操作大約需要10個時鐘周期。如果輸出的數據位寬為16位,那么數據由FPGA向外傳輸的速率要小于160 MHzo控制模塊在讀寫內存條的時候控制數據模塊來實現數據率為時鐘速度的兩倍,數據模塊使用兩個時鐘一個是系統時鐘一個是2倍的系統時鐘。

因為DDR SDRAM的控制相對復雜,我們可以使用內存條的vefilog模型,通過對內存條的vefilog仿真,我們可以知道自己程序的正確性,圖8為modelsim中的仿真波形。如果仿真過程正確,我就可以對程序進行編譯,布局布線,然后下載到FPGA中,由于布局布線的延時,輸出的信號波形與仿真波形不一致,此時,可以通過調整FPGA內部的鎖相環來調整時序,實現對內存條的控制。

4 結束語

通過介紹內存條的工作原理,以及內存條電路設計時的注意事項的介紹,我們可以更合理的實現FPGA與內存條的互連。最后,給出FPGA內部對內存條控制的方法,以及給出仿真波形,實現對內存條的控制。實現FPGA對DDRSDRAM內存條的控制,可以實現大容量高速的數據存儲,在工程中的得到廣泛的應用。

評論