從4004到core i7——處理器的進化史-CPU構成零件-5

這個單元有個神奇的性質:當C=0時,A和B是斷開的;當C=1時,A信號能夠不損失電平地傳播到B!

本文引用地址:http://www.104case.com/article/221767.htm這種單元在特定的場景下特別有用。例如總線結構中,各個輸出端口就通過一個這樣的傳輸門接到總線上,C一般接片選(CS)信號。這樣就能夠不沖突地通信了!

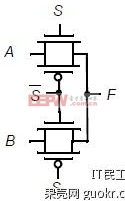

再比如這個2-1數據選擇器

3.動態邏輯(dynamic logic)

對,你沒有看錯,確實存在動態邏輯。

之前我講的都是靜態邏輯。回憶一下,這意味著每個信號都通過低阻回路上拉到VDD或者下拉到地。而在動態邏輯中,信號還可以用存在電容上的電荷導致的電平來表示。我們還是看一張總結這種設計模式的圖:

注意,上圖中已經出現了時鐘(CLK)信號。一個組合邏輯電路中出現時鐘很詭異吧。CL并不是專門接的,利用的就是后一級的門級電容!

這個電路的工作分成兩個階段:

第一個階段,CLK=0,只有上面的PMOS導通。CL被強制沖到高電平。

第二個階段,CLK=1,只有下面的NMOS和PDN導通。如果PDN中有同路,那么CL就被放電,否則就應該停留在高電平。

不停地重復著兩個階段,就可以使這個電路正常工作!

我們還是來看看這個電路的利與弊吧。

Pros:

1.比例無關的邏輯!由于CLK導致的互補性,這個電路的輸出是比例無關的!

2.無靜態功耗。很明顯,在理想情況下這個電路沒有靜態通路。

3.快!!!這是動態邏輯最主要的特點,理由和偽NMOS邏輯一樣。沒有了PUN,輸入電容小,自然就快了。

4.晶體管數少。理由同上。

怎么樣,動態邏輯很牛吧。不過它的限制也是很明顯的。

Cons:

1.易受不理想因素的影響。電容上的電荷常常要受漏電的影響。一個動態邏輯門的輸入電容一半在fF(10^-15F)級別,這么小的電容即使是反偏PN結的漏電流也會對它造成重大影響。如果電容上的電容存不住,自然就會產生錯誤。

2.需要復雜的外電路配合。這主要是CLK信號的生成。

評論