從4004到core i7——處理器的進化史-CPU構(gòu)成零件-5

前面我說過,要順帶介紹一下除了CMOS之外的邏輯電路。所以下面我們看一看都有哪些選擇,以及各自的利弊吧。

本文引用地址:http://www.104case.com/article/221767.htm

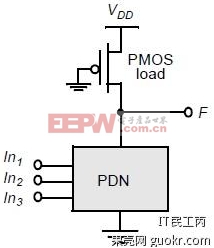

這種電路中,一個總是導(dǎo)通的PMOS代替了CMOS中的PUN。

Pros:

1.速度快。前面講過,R與C的乘積決定了IC整體的速度。如果我們干掉PUN自然就減小了C,提高了速度。

2.管子少。一目了然。這個優(yōu)點在追求面積最小的時候很有用。

Cons:

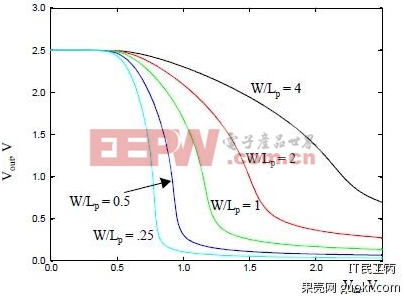

1.電壓傳輸特性不理想,比例相關(guān)的邏輯。這里的PMOS的作用就相當(dāng)于漏極開路輸出中的上拉電阻,有它在,輸出的下拉就沒辦法到0了。另外,偽NMOS的電壓傳輸特性曲線見下圖,由于PDN中的管子在大部分區(qū)域都工作在放大狀態(tài)所以曲線比較平緩,導(dǎo)致其噪聲容限很小。

2.有靜態(tài)功耗。這就很明顯了吧,當(dāng)PDN接通的時候電流總是需要從PMOS管子上流過。

偽NMOS的最著名的例子就是intel 4004。不過intel可是是迫不得已,因為當(dāng)時PMOS器件還不成熟呢......

那有沒有偽PMOS邏輯呢?答案是一般不這么設(shè)計,因為NMOS器件的等效電阻總是比相同參數(shù)的PMOS小一些,能提供更好的低電平輸出(相對于偽PMOS邏輯的高電平輸出)。

2.傳輸門邏輯(transmission gate logic)

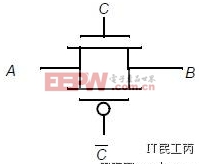

所謂傳輸門是指下面接法的一對NMOS和PMOS

評論