范式級技術革命!合見工軟年度發布多款國產自研EDA與IP解決方案

2025年6月24日,中國數字EDA/IP龍頭企業上海合見工業軟件集團有限公司(簡稱“合見工軟”)今日在上海召開了“2025合見工軟新產品發布會暨技術研討會”,會上展示了下一代國產EDA技術的重大革新進展,并正式發布了多款國產自主自研EDA及IP產品,助力我國自研EDA和IP產品從國產化替代到國際標桿技術的進階。

本次合見工軟正式發布的五款創新產品包括:

● 數字驗證下一代硬件產品:

o 下一代全場景驗證硬件系統UniVista Unified Verification Hardware System Gen2(UVHS-2)

● 國產數字仿真調試EDA重大進展:

o 下一代全功能高性能數字仿真器UniVista Simulator Plus (UVS+)

o 下一代全功能高效能數字驗證調試平臺UniVista Debugger Plus (UVD+)

● 全國產自主知識產權高速接口IP解決方案:

o 推動智算互聯的超以太網IP解決方案UniVista UEC MAC IP

o 先進工藝多協議兼容、集成化傳輸接口SerDes IP解決方案

合見工軟現有產品已覆蓋數字芯片EDA工具、系統級工具及高端IP,是國內唯一一家可以完整覆蓋數字芯片驗證全流程,DFT可測性設計全流程,并同時提供先進工藝高速互聯IP的國產EDA公司。自成立以來,合見工軟一直以國際先進水平為目標,多產品線并行研發,為中國半導體企業提供了芯片硅前和硅后的高性能EDA工具和IP解決方案。

此次發布的下一代EDA戰略,合見工軟將數字驗證最核心的基礎工具——數字仿真/調試器,及支持大規模芯片設計的高端硬件驗證平臺,均實現了架構級迭代創新,是國產EDA技術創新的重大進展,多項性能比肩國際標桿水平,目標打破數字高端大芯片驗證EDA的國際廠商壟斷。

同時,合見工軟已在國內自研IP領域取得了快速的技術進展和客戶增長,在國內自主自研高速接口IP的市場份額中已居前列。目前,合見工軟的高速接口IP解決方案已實現了國產化技術突破,支持國內外先進工藝,并得到多家商業客戶的成功流片和數百家客戶的商業部署。合見工軟的智算芯片互聯IP解決方案,覆蓋國內外先進標準,助力智算、HPC、通信、自動駕駛、工業物聯網等領域大算力芯片的性能突破及爆發式發展。尤其在當前國際先進EDA工具和制程受限的情況下,合見工軟對高端芯片設計企業的產品與技術支持,助力了中國超算和AI類芯片企業打造自主可控的上下游供應鏈。

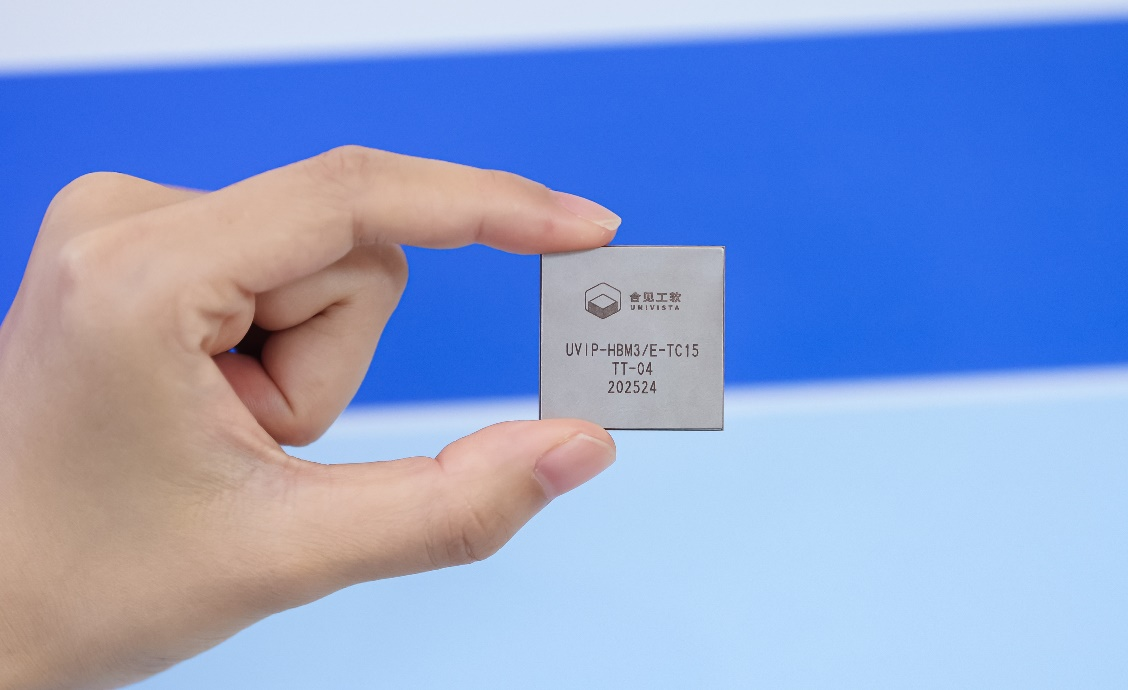

特別值得一提的是,在此次發布會上,合見工軟宣布已經成功點亮HBM3/E測試芯片,基于標準電壓實現高達9600MT/s的數據傳輸。合見工軟提供高性能自研 HBM3/E IP控制器和PHY整體解決方案,控制器支持超低的讀寫延遲可以根據客戶讀寫Pattern做定制化設計,加強的抗衰減和Deskew能力可以應對各種復雜場景設計,內置處理器可以靈活支持多種Training算法,完整的2.5D interposer和SIPI分析服務可以幫助客戶通過端到端優化提升HBM3/E系統運行速度。自研HBM3/E控制器和PHY,廣泛支持業界的各種顆粒,幫助客戶在實際的系統中真正實現高性能。

先進工藝HBM3/E測試芯片

在地緣政治和技術壁壘不斷加劇的時代,中國半導體企業面臨著芯片設計與系統設計工具的重重技術封鎖與挑戰,考驗著國產EDA企業的真正技術水平與發展韌性,只有真正經過用戶打磨驗證的EDA工具,才能建立可持續的商業生態,與國際壟斷企業開啟真正的技術競賽。特別是此次美國EDA斷供的全面危機之時,合見工軟在此前正式向用戶免費開放關鍵產品試用與評估服務,在當前國產工具普遍“缺乏市場驗證”的挑戰下,證明了合見工軟產品在規模化應用和強大技術支持能力,只有真正經過用戶打磨驗證的工具才能具備持久的競爭力。

EDA與IP是中國科技自主化進程中的關鍵一戰,合見工軟以四年近40款產品的創新速度、硬核的技術實力,贏得了客戶的信任與國內集成電路行業的廣泛認可,同時引領了中國EDA企業發展與生態建設的新態勢。

合見工軟產品布局

數字驗證核心工具重大革新:全功能數字仿真調試平臺UVS+/UVD+

合見工軟今日宣布數字芯片驗證的核心仿真調試工具已取得重大進展,正式發布國產自研下一代全功能高性能數字仿真器UniVista Simulator Plus (UVS+)和下一代全功能高效能數字驗證調試平臺UniVista Debugger Plus (UVD+)。新一代仿真器UVS+打造全國產一站式驗證流程,全自研架構,并支持國產服務器生態,可比肩國際領先廠商的仿真、編譯及波形處理的先進性能,大幅加速驗證流程;全面覆蓋支持現代芯片驗證所需的數字仿真功能和各項特殊應用場景需求。新一代調試平臺UVD+集成更多高階功能,提供全場景調試能力,創新的數據處理架構提升驗證調試效率,并打造全新視覺觀感,多維提升調試體驗。

2021年10月,合見工軟就推出了國內首款自主自研的商用級數字仿真器,正式打破了國際EDA高端仿真工具的壟斷,對EDA國產化意義重大。三年多以來,UVS系列已經過百萬量級客戶實戰項目用例打磨淬煉和持續迭代優化,已在50+個關鍵芯片項目中成功應用,得到了國內頭部客戶的認可,積累了豐富的行業經驗。

合見工軟現可提供高性能自主可控的國產數字驗證EDA全流程工具,此次發布的數字仿真器UVS+和數字驗證調試平臺UVD+是合見工軟數字EDA驗證全流程的核心基礎工具,結合最新發布的下一代全場景驗證硬件系統UVHS-2,以及數據中心級全場景超大容量硬件仿真加速驗證平臺UVHP,單系統先進原型驗證平臺PD-AS,虛擬原型設計與仿真工具套件V-Builder/vSpace,驗證管理軟件VPS等產品組合,全面覆蓋從早期虛擬架構設計建模、中期硬件仿真加速、中期子系統級軟件到后期全芯片級原型驗證的全場景需求。

合見工軟國產數字驗證EDA全流程工具

合見工軟聯席總裁郭立阜表示:“國產EDA工具鏈的自主可控對于打造安全、高效、可持續的芯片產業環境至關重要,而芯片設計驗證占據總設計周期的70%以上,直接影響產品上市時間和質量,只有高性能與可靠性并重的驗證工具,才是保障客戶項目成功的關鍵。合見工軟數字仿真及調試工具經過與國內頭部芯片設計企業緊密合作,歷經三年淬煉迭代,第二代UVS+與UVD+工具平臺帶來性能上的飛躍,全自研架構自主可控帶來可靠性的全面提升,提升供應鏈韌性,為中國芯片設計項目保駕護航,抵御外部風險,為‘中國芯’的創新提供沃土。”

客戶評價:

中興微電子有線系統部部長賀志強表示:“作為合見工軟的深度戰略合作伙伴,我們在2021年自第一代UVS/UVD誕生時起,就將其應用于項目的驗證流程。四年來,我們與合見工軟的研發技術團隊,共同見證了這款國產EDA工具經過無數次打磨迭代后的全面系統性升級。并很高興的看到第二代UVS+/UVD+所取得的諸多技術進展和架構革新。

UVS+在復雜SoC場景的對比測試中展現出與國際領先水平相當的穩定性和性能,在近期芯片回歸測試中體現了扎實的軟件產品化成熟度;同時,UVD+打造了創新的GUI設計,其直觀的調試工作流和智能診斷能力為調試工作提供了更高效的設計洞察,顯著提升了問題根因定位的精準度和效率。

這些進步標志著國產驗證工具正加速從‘可用’向‘好用’的技術拐點邁進。面對當前高復雜度芯片設計的挑戰,我們期待合見工軟持續深耕本土化場景創新,在保持技術演進勢頭的同時,進一步強化對中國芯片設計流程的深度適配,為產業構建自主可控、高效協同的工具鏈新生態。”

碾壓級動力提升:下一代全場景驗證硬件系統UVHS-2發布!

合見工軟發布下一代全場景驗證硬件系統UniVista Unified Verification Hardware System Gen2(UVHS-2),最大可級聯高達192片AMD Versal? Premium VP1902 Adaptive SOC,為大規模 ASIC/SOC 軟硬件驗證提供多樣化應用場景設計,可廣泛適用于 AI 智算、數據中心、HPC 超算、智能駕駛、5G 通信、智能手機、PC、IoT 等各類芯片的開發過程。作為高效的軟硬件驗證解決方案,UVHS-2能夠大幅縮短芯片驗證周期,加速芯片上市進程。

2023年合見工軟發布了第一代全場景驗證硬件系統 UVHS,經由市場打磨,已在多家客戶的主流大芯片項目中部署,實現了多家客戶全芯片級別的軟硬件驗證并協助客戶成功流片迭代,客戶包括中興微電子、燧原科技、清華大學、達摩院玄鐵、北京開源芯片研究院等。

相較于上一代產品 UVHS,UVHS-2在多個關鍵性能指標上實現了顯著提升:容量提升超 2 倍,運行性能提升 1.5-2 倍,調試容量和帶寬提升 4 倍。其基于 AMD Versal? Premium VP1902 Adaptive SOC,FPGA 核心性能最高可達 100MHz。在擴展規模方面,UVHS-2 系統最大級聯規模可達 192 顆,邏輯門數量超過 150 億門。借助合見工軟核心技術——全局時序驅動的自動分割引擎,即便在超大規模系統場景下,仍能保持 10MHz 以上的 FPGA 跨片性能。UVHS-2也提供充足且可配置的互聯通道,能夠靈活支撐系統擴展需求。

合見工軟首席技術官賀培鑫博士在發布會演講中表示:“從2022年發布第一款時序驅動的原型驗證平臺,到如今性能可比肩國際標桿產品的下一代全場景硬件驗證系統UVHS-2,合見工軟的硬件驗證產品線在三年來保持著持續高速的研發創新步伐,并得到了廣泛的客戶認可和商業部署。此次發布的UVHS-2平臺從核心處理器升級、級聯規模和雙模架構創新提升等方面,為用戶帶來了更大容量、更高效率、更強性能三大核心優勢。UVHS-2提供了更多新的驗證范式躍遷,實現更靈活的軟硬件協同仿真,顯著加速驗證周期,幫助客戶提升流片成功率。現在,合見工軟已實現從IP級到超大規模系統級驗證的全線覆蓋,全面支撐中國數字芯片設計與驗證自主可控。”

客戶評價:

芯原微電子GPU產品研發副總裁張慧明表示:“合見工軟的UVHS平臺是芯原Vivante GPU IP全流程交付流程中的重要驗證平臺。其超大容量FPGA原型驗證能力幫助我們構建了從IP集成、系統驗證到軟件生態的一站式解決方案,為客戶提供可快速落地的GPU參考設計套件。該平臺不僅支持早期GPU系統級環境搭建,更實現了硬件與軟件開發的全周期協同,在AI智算、智能汽車等領域大幅縮短了我們客戶的項目周期。隨著算力芯片復雜度提升,基于與合見工軟的戰略合作,芯原將與國內EDA企業共同探索,加速下一代Chiplet異構計算平臺的規模化落地。”

推動智算互聯:下一代核心協議IP支撐未來網絡基建

合見工軟今日發布超以太網IP解決方案UniVista UEC MAC IP,大幅提升網絡性能和可靠性,推動智算互聯從“通用連接”向“高性能計算網絡”的進化,重塑AI基礎設施格局,更好的為AI/ML、HPC(高性能計算)和云數據中心場景提供底層支撐。合見工軟超以太網UEC MAC IP現已成功在高性能計算、人工智能AI、數據中心等復雜網絡領域IC企業芯片中部署。

隨著時代的發展,智算芯片在人工智能和高性能計算領域的應用取得了卓越的進展,但同時也對智算芯片的組網規模、帶寬密度、多路徑、對擁塞的快速反應以及數據流執行度的相互依賴等方面提出了更高的要求。

合見工軟創新推出的超以太網 UEC MAC IP符合國際超以太網聯盟(Ultra Ethernet Consortium,簡稱UEC)協議的物理層和鏈路層的IP標準,在傳統以太網IP的基礎上,擴展支持了UEC的物理層和鏈路層的功能,尤其是LLR(鏈路層重傳)和CBFC(基于信用的流控)的功能,實現了網絡的無損傳輸以及可靠性的提升。

同時,合見工軟UEC MAC IP的推出,可與原有的智算網絡IP解決方案UniVista RDMA IP和針對智算網絡Scale-up應用的 ETH-X傳輸層協議解決方案UniVista PAXI IP相互協同,進一步擴大了合見工軟在智算芯片互聯IP技術領域的優勢。

合見工軟副總裁楊凱表示:“UEC是下一代數據中心和AI計算網絡的核心協議,其重要性不僅體現在技術革新上,更對全球算力基礎設施的競爭格局產生深遠影響,特別是對中國產業來說,急需高性能的智算網絡方案來推動智算集群的性能的提高。合見工軟創新推出的超以太網 UEC MAC IP,實現了網絡可靠性的大幅提升,推動傳統以太網升級為超算級網絡,支撐未來AGI時代我國的算力和網絡基礎設施建設。合見工軟志在將真正自主可控的IP產品和EDA產品一起為客戶提供完整可靠的芯片設計方案。”

合見工軟的高速接口IP解決方案已實現了國產化技術突破,引領智算、HPC、通信、自動駕駛、工業物聯網等領域大算力芯片的性能突破及爆發式發展。

高端芯片的自主可控:先進接口IP方案助力流片成功

合見工軟今日發布國產自主研發支持多協議的32G SerDes PHY 解決方案UniVista 32G Multi-Protocol SerDes IP (簡稱UniVista 32G MPS IP)。該多協議PHY產品可支持PCIe5、USB4、以太網、SRIO、JESD204C等多種主流和專用協議,并支持多家先進工藝,成功應用在高性能計算、人工智能AI、數據中心等復雜網絡領域IC企業芯片中部署。

UniVista 32G MPS IP由硬化模塊(PMA/SerDes)和RTL模塊(Raw PCS)組成,支持高達 32 Gbps 的數據傳輸速率(例如PCIe Gen5速率下32.0GT/s),全面支持 PCIe Gen1-5、USB4、以太網(25GKR、10GKR)、SRIO、JESD204C等多種主流和專用協議。其SerDes接口更提供多種數據位寬選項,具備獨立的發送和接收同步時鐘,并包含訓練功能。UniVista MPS IP可充分滿足數據中心、高性能計算、網絡設備等應用領域對高速互連的嚴苛需求,經過嚴格驗證與深度評估,可在各種應用場景中均表現出優異的穩定性和可靠性。

合見工軟副總裁劉矛表示:“在數據量以指數級增長的時代,高性能計算、智算、數據中心等等應用都對芯片底層互聯與外部數據通信提出了更嚴苛的要求,高速串行通信SerDes作為互聯接口的核心技術,對國產高端數字芯片的自主可控需求至關重要。合見工軟UniVista 32G MPS IP解決方案,憑借高性能、高穩定性、低能耗和靈活配置,滿足高速數據傳輸需求,為客戶提供高可靠性的先進接口IP整體解決方案,經過實際驗證,可幫助客戶在面對新的接口實現應用時,大幅提高性能和改善能效,實現一次性流片成功,縮短產品的上市周期。合見工軟志在將真正自主可控的IP產品和EDA產品一起為客戶提供完整可靠的芯片設計方案。”

合見工軟目前可提供的廣泛IP解決方案包括:UniVista PCIe Gen5完整解決方案,以太網(Ethernet)、靈活以太網(FlexE)、Interlaken等多種高速互聯接口控制器,ETH-X傳輸層協議(PAXI)IP和VIP產品,智算網絡解決方案RDMA IP,Memory 接口HBM3/E、DDR5 、LPDDR5 IP,HiPi標準IP/VIP,針對先進封裝芯粒(Chiplet)集成的關鍵標準UCIe IP,并實現國產首個跨工藝節點的UCIe IP互連技術驗證,在采用臺積電N6和三星SF5工藝制造的UCIe測試芯片之間成功完成互操作性測試,實現D2D和C2C互連應用。

評論