FOPLP 熱潮加劇:ASE、Powertech 擴張;臺積電據報籌備 2026 CoPoS 試驗線

根據 經濟日報 的報道,扇出型板級封裝(FOPLP)被視為先進封裝的下一個主流技術。關鍵行業參與者——包括晶圓巨頭臺積電、半導體封裝和測試領導者 ASE 以及存儲封裝巨頭 Powertech——都在積極投資該領域,以滿足來自 NVIDIA 和 AMD 等主要客戶對高性能計算(HPC)芯片封裝日益增長的需求。

本文引用地址:http://www.104case.com/article/202506/471405.htm報道中引用的行業消息人士指出,與晶圓級方法相比,板級扇出封裝提供了更大的基板面積,并支持異構集成,有助于進一步小型化消費電子產品。

TSMC

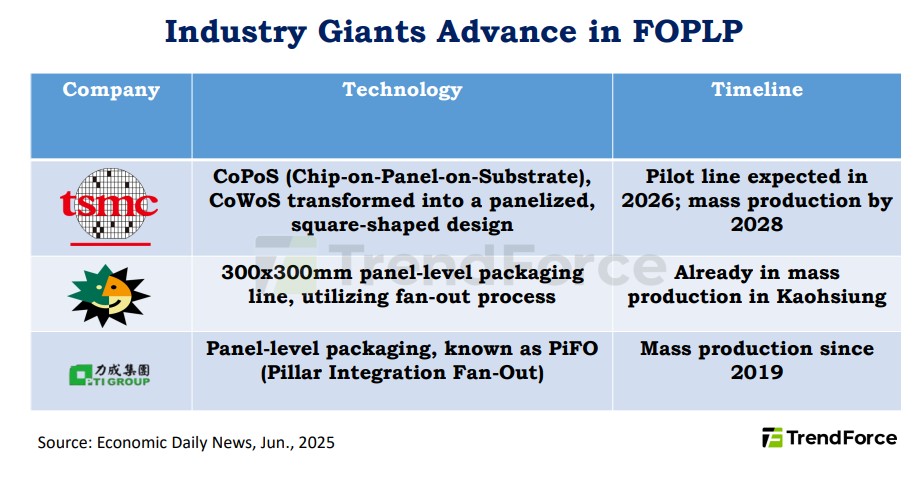

報告稱,臺積電的扇出型面板級封裝(FOPLP)技術據稱為 CoPoS(芯片面板基板封裝),計劃在嘉義生產。報告預計,2026 年將建立一條試驗線。

如報告所述,臺積電的 CoPoS 技術主要面向人工智能和高性能計算(HPC)應用。消息人士表示,預計到 2028 年將實現大規模生產。該工藝將 CoWoS 封裝轉換為面板化的方形設計,報告指出這將顯著提高芯片產量。

值得注意的是,MoneyDJ 強調英偉達可能是臺積電 CoPoS 技術的第一個大客戶,而經濟日報指出 CoPoS 擴展了為博通設計的 CoWoS-R,以及為英偉達和 AMD 設計的 CoWoS-L。

與此同時,正如經濟日報所報道的,臺積電在其北美技術研討會上推出了一種新的 CoWoS 技術,其光罩尺寸為 9.5 倍,計劃于 2027 年開始大規模生產。據 Anue 報道,這標志著從目前 CoWoS-L 的 3.3 倍光罩尺寸和去年推出的 8 倍版本的重大升級,能夠將 12 個或更多的 HBM 堆疊集成到單個封裝中。

正如經濟日報所表明的,ASE 已經在高雄運營一條大規模生產的板級封裝線,使用 300x300 毫米的板和扇出工藝。

Powertech

該報告還指出,Powertech 在這個領域最為活躍,早在 2019 年就實現了大規模生產。其扇出面板級封裝技術,稱為 PiFO(柱集成扇出),正如報告所暗示的那樣,在技術上與 TSMC 的 CoPoS 類似。

評論