閃存,是如何工作的?

閃存使用網格中的浮柵晶體管存儲數據。寫入過程中,電子通過量子隧穿效應被捕獲,從而改變單元電壓。擦除操作使用塊級電壓脈沖重置電荷。由于絕緣氧化層的存在,數據即使在斷電的情況下也能保存,但反復寫入會降低單元的性能。

本文引用地址:http://www.104case.com/article/202505/470091.htm浮柵晶體管如何存儲數據?

浮柵將電子捕獲在氧化層之間,從而改變晶體管的閾值電壓。這種二進制狀態 (0/1) 通過感測電流來讀取。與 DRAM 不同,電荷無需刷新周期即可保持完整。

每個閃存單元的核心都是一個 MOSFET,它帶有一個夾在控制柵極和基板之間的附加浮柵。編程時,高電壓 (15-20V) 迫使電子通過 Fowler-Nordheim 隧穿效應穿過隧道氧化物。這些被捕獲的電子會提高晶體管的閾值電壓,該電壓可在讀取過程中檢測到。實際上,這就像往水桶(浮柵)里注水,除非強行倒空,否則水不會漏。現代 3D NAND 將單元垂直堆疊,并使用電荷捕獲閃存 (CTF) 來減少電子泄漏。但是,如果氧化物降解會發生什么?就像生銹的管道一樣,損壞的絕緣層會導致電荷泄漏,從而導致數據損壞。制造商使用糾錯碼 (ECC) 和更嚴格的電壓裕度來解決這個問題。

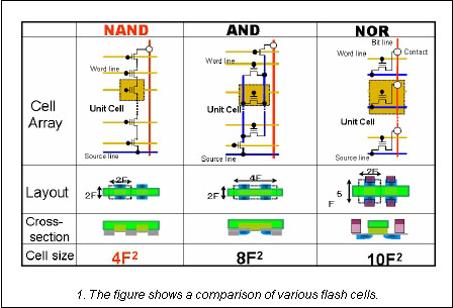

NAND 和 NOR 閃存架構有什么區別?

NOR 閃存使用并行單元進行隨機訪問,非常適合固件。NAND 閃存將單元串聯排列以實現高密度存儲,優先考慮寫入/擦除速度而不是直接尋址。

NOR 的并行結構允許字節級讀取,使其行為類似于傳統 RAM,但具有非易失性。但是,擦除塊很大(64-128KB),寫入速度很慢。相反,NAND 將 32-64 個晶體管串聯起來,從而實現頁面級操作(4-16KB)和更便宜的高密度設計。可以將 NOR 想象成一個圖書館,您可以在其中直接獲取任何書籍(字節),而 NAND 則是一條傳送帶 —— 您必須一次處理整個盒子(頁面)。從技術上講,由于單元結構更簡單,NAND 實現了更高的耐用性(100K 次,而 NOR 為 10K)。對于 SSD,制造商更喜歡 3D TLC NAND,因為它具有每 GB 成本優勢,盡管寫入速度較慢。一個關鍵的權衡:NOR 的延遲是微秒,而 NAND 的隨機訪問延遲為毫秒。

數據寫入和擦除操作是如何進行的?

寫入操作通過隧穿效應注入電子,而擦除操作則利用熱載流子注入來釋放電荷。兩者都需要高壓電路,從而隨著時間的推移對氧化層施加應力。

在編程期間,電壓差(控制柵極上為 7-10V,襯底上為 0V)會產生足夠強的電場,將電子推過隧道氧化物。擦除時,需要施加 20V 的襯底偏壓,從而逆轉這一過程,將電子拉回。但問題在于:擦除會影響整個塊(256KB-4MB),而不是單個字節。為什么?因為在每個單元上施加如此高的電壓需要不切實際的電路。打個比方:重新粉刷整面墻(塊)比修補散落的磚塊(字節)更容易。SSD 通過過度配置來減輕擦除開銷——保留額外的單元以分散磨損。但是,過多的寫入仍然會在氧化物中產生電子陷阱,從而永久性地提高單元的閾值電壓。

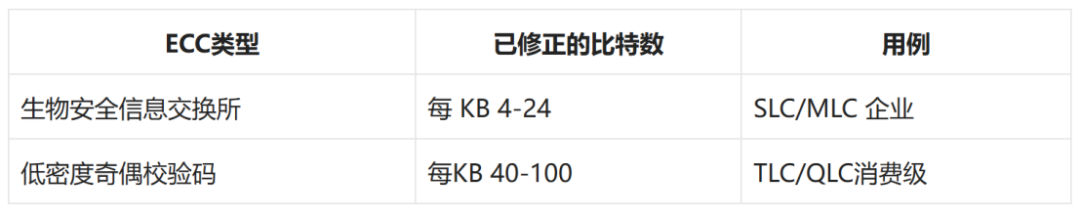

糾錯在閃存壽命中起什么作用?

ECC 算法可以檢測/糾正由電荷泄漏或寫入干擾引起的位錯誤。像 LDPC 這樣的高級方案可以補償老化單元帶來的問題,但會增加延遲。

由于閃存單元要承受編程/擦除周期,因此氧化物磨損會增加誤碼率 (BER)。SLC(1 位/單元)可能使用基本 BCH 碼承受 10 萬次循環,而 TLC(3 位/單元)需要強大的 LDPC 碼承受 10000 次循環。將 ECC 想象成數據的拼寫檢查 - 小錯誤會自動修復,但太多拼寫錯誤則需要重寫整個段落(數據重試)。從技術上講,LDPC 使用概率模型來猜測原始電荷,但這需要更多的計算能力。禁用 ECC 以提高速度(例如,在 DIY SSD 項目中)可能會導致靜默數據損壞。除了軟件之外,跨芯片的 RAID 式冗余等硬件技術也有幫助。你知道嗎?QLC NAND 中 1% 的 BER 在 3 年后可能會激增至 25% - 因此消費級 SSD 通過積極的 ECC 來隱藏這一點。

磨損均衡如何延長閃存壽命?

損耗均衡技術利用固件映射將寫入操作均勻分布到各個塊。動態和靜態方法可防止「熱點」過早損壞單元。

閃存控制器通過邏輯到物理地址表跟蹤每個塊的擦除次數。動態損耗均衡將新寫入重定向到較少使用的塊,而靜態損耗均衡則定期移動陳舊數據。這就像汽車輪胎的旋轉一樣——均勻的磨損可以最大化總里程。例如,具有 3K 耐久性和 10% 過度配置的 1TB SSD 可以處理 3.3PB 的寫入量,相當于 20 年內每天寫入 45GB。但實際上,由于小規模隨機寫入導致的寫入放大,控制器通常會更早出現故障。專業提示:使用 TRIM 命令標記已刪除的文件,讓控制器在空閑時間預擦除塊。但是,損耗均衡無法解決固有的單元性能退化問題——最終,所有 NAND 都會變得不可靠。

為什么閃存單元的性能會隨著時間推移而下降?

反復的隧穿效應會對氧化層造成應力,形成阻礙電荷移動的電子陷阱。累積的損傷會導致漏電流增加,直至電池無法維持規定的電壓水平。

每個編程/擦除周期都會在二氧化硅晶格中產生缺陷。最初,ECC 會掩蓋這些錯誤,但最終陷阱會累積,使單元變得「粘滯」——它們要么無法完全充電(編程干擾),要么泄漏太快(數據保留失敗)。可以把它想象成花園水管:細小的裂縫會導致小泄漏(可糾正錯誤),但完全破裂則需要更換(壞塊)。從技術上講,磨損的 QLC 中的數據保留時間會從 10 年(新的 SLC)下降到數月。高溫環境會加速這一過程——數據中心會主動將 SSD 冷卻至 15°C 以下。

評論