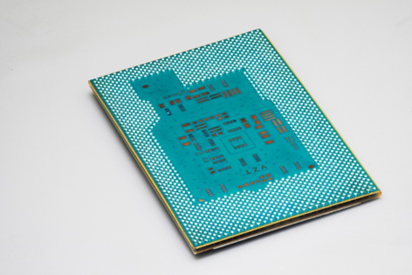

一文看懂英特爾的制程工藝和系統級封裝技術

一文帶你看懂英特爾的先進制程工藝和高級系統級封裝技術的全部細節...

1. 制程技術

Intel 18A英特爾18A制程節點正在按既定計劃推進,首個外部客戶的流片工作將于2025年上半年完成。Intel 18A預計將在2025年下半年實現量產爬坡,基于該制程節點的首款產品,代號為Panther Lake,將于2025年年底推出,更多產品型號將于2026年上半年發布。【英特爾新篇章:重視工程創新、文化塑造與客戶需求;英特爾發布2025年第一季度財報】

與Intel 3制程工藝相比,Intel 18A的每瓦性能預計提升15%,芯片密度預計提升30%。【Intel 18A | See Our Biggest Process Innovation】

Intel 18A應用了兩項關鍵技術突破:RibbonFET全環繞柵極晶體管技術與PowerVia背面供電技術。【Intel 18A | See Our Biggest Process Innovation】

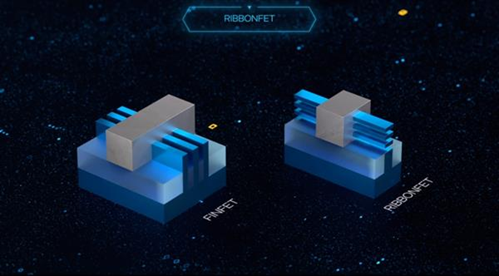

l RibbonFET全環繞柵極晶體管:芯片制程工藝不斷進化的進程中,隨著芯片密度不斷攀升,由于漏電問題導致的發熱現象似乎成為一種“魔咒”,成為前進道路上的主要障礙之一。而RibbonFET正是應對這一挑戰的有效解決方案。

通過英特爾十多年來最重要的晶體管技術創新之一,英特爾實現了全環繞柵極(GAA)架構,以垂直堆疊的帶狀溝道,提高晶體管的密度和能效,實現電流的精準控制,在實現晶體管進一步微縮的同時減少漏電問題發生。

此外,RibbonFET提高了每瓦性能、最小電壓(Vmin)操作和靜電性能。無論在何種電壓下,都能提供更強的驅動電流,讓晶體管開關的速度更快,從而實現了晶體管性能的進一步提升。RibbonFET 還通過不同的帶狀寬度和多種閾值電壓(Vt)類型提供了高度的可調諧性,為芯片設計帶來了更高的靈活性。

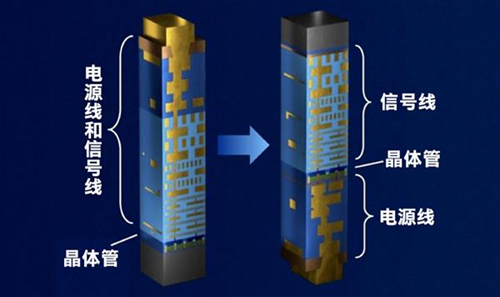

l PowerVia背面供電:隨著越來越多的使用場景都需要尺寸更小、密度更高、性能更強的晶體管來滿足不斷增長的算力需求,而混合信號線和電源一直以來都在“搶占”晶圓內的同一塊空間,從而導致擁堵,并給晶體管進一步微縮增加了難度。

PowerVia背面供電技術應運而生,通過將粗間距金屬層和凸塊移至芯片背面,并在每個標準單元中嵌入納米級硅通孔 (nano-TSV),以提高供電效率。這項技術實現了ISO功耗效能最高提高4%,大大減少了固有電阻(IR)下降的槍口,并提升標準單元利用率5%至10%。

2024年2月,英特爾拓展了制程技術路線圖:【制程節點,團隊亮相】

l Intel 14A采用High-NA EUV技術,預計將于2027年前實現大規模量產。

l 英特爾還計劃一路推出節點的演進版本,滿足客戶的不同需求。其中,P版本實現了至少5%的性能提升(Intel 18A-P);E版本進行了功能拓展,如射頻和電壓調整等(Intel 16-E、Intel 3-E、Intel 14A-E);T版本通過采用硅通孔,針對3D堆疊進行了優化(Intel 3-T、Intel 3-PT)。

2. 封裝技術

先進封裝的意義

半導體先進封裝技術能夠在單個設備內集成不同功能、制程、尺寸、廠商的芯粒(chiplet),以靈活性強、能效比高、成本經濟的方式打造系統級芯片(SoC)。因此,越來越多的AI芯片廠商青睞這項技術。【英特爾先進封裝:助力AI芯片高效集成的技術力量】

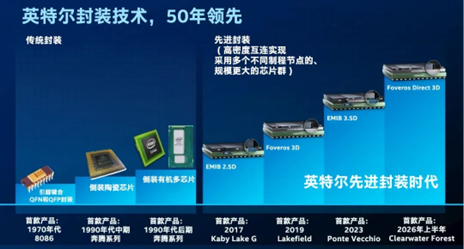

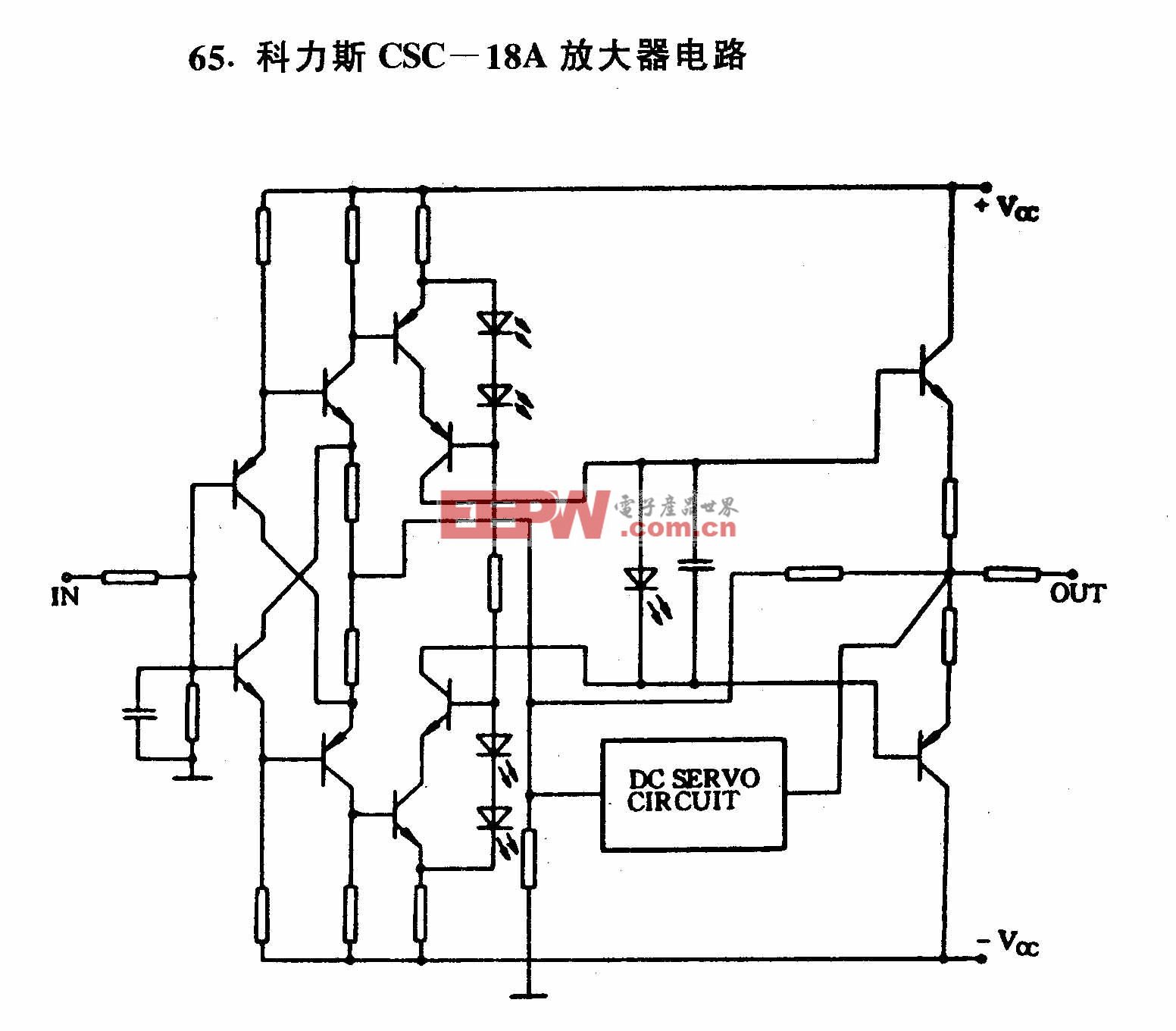

英特爾先進封裝解決方案

英特爾代工的先進系統封裝及測試(Intel Foundry ASAT)的技術組合,包括FCBGA 2D、FCBGA 2D+、EMIB 2.5D、EMIB 3.5D、Foveros 2.5D & 3D和Foveros Direct 3D等多種技術。【英特爾先進封裝:助力AI芯片高效集成的技術力量】

左上:FCBGA 2D、右上:EMIB 2.5D、

左下:Foveros 2.5D & 3D、右下:EMIB 3.5D

l FCBGA 2D是傳統的有機FCBGA(倒裝芯片球柵格陣列)封裝,適用于成本敏感、I/O數量較少的產品。

l FCBGA 2D+在此基礎上增加了基板層疊技術(substrate stacking),能夠減少高密度互連的面積,降低成本,特別適合網絡和交換設備等產品。

l EMIB(嵌入式多芯片互連橋接)2.5D技術通過基板上的微型硅橋連接芯片,適用于高密度的芯片間連接,在AI和高性能計算(HPC)領域表現出色。

l EMIB 3.5D則在此基礎上引入了3D堆疊技術,芯片可以垂直堆疊在有源或無源的基板上,再通過EMIB技術連接,增加了堆疊的靈活性,能夠根據IP的特性選擇垂直或水平堆疊,同時避免使用大型的中介層。

l Foveros 2.5D和3D技術采用基于焊料的連接方式,而不是基底連接,適合高速I/O與較小芯片組分離的設計。

l Foveros Direct 3D技術則通過銅和銅直接鍵合,實現更高的互連帶寬和更低的功耗,從而提供卓越的性能。

值得注意的是,這些技術并非互斥,而是在一個封裝中可以同時采用,為復雜芯片的設計提供了極大的靈活性。在商業層面,這體現了英特爾對封裝細分市場的重視。

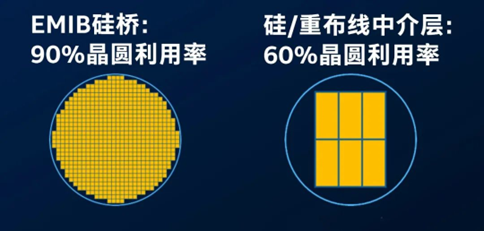

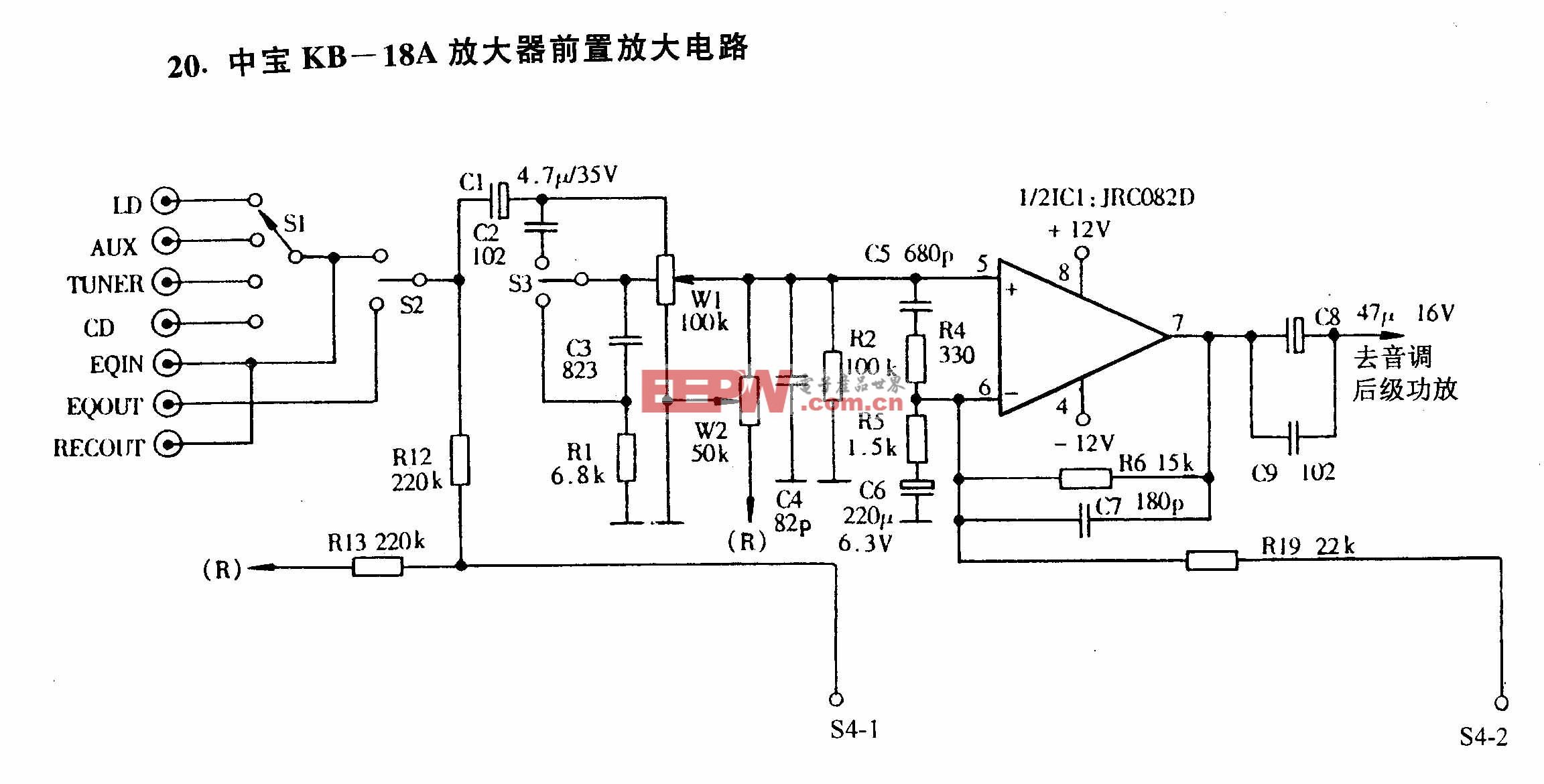

EMIB:AI芯片封裝的理想選擇

針對AI芯片的先進封裝需求,與業界其它晶圓級2.5D技術,例如硅中介層、重布線層(RDL)相比,EMIB 2.5D技術具有諸多優勢:【英特爾先進封裝:助力AI芯片高效集成的技術力量】

l 成本效益:EMIB技術采用的硅橋尺寸非常小,相比于傳統的大尺寸中介層,制造時能更高效地利用晶圓面積,減少空間和資源的浪費,綜合成本更低。

l 良率提升:EMIB技術省略了晶圓級封裝(wafer level assembly)這一步驟,減少了模具、凸點等復雜工藝帶來的良率損失風險,從而提高了整體生產過程的良率。

l 生產效率:與晶圓級技術相比,EMIB技術的制造步驟更少、復雜度更低,因此生產周期更短,能夠為客戶節省寶貴的時間。在市場動態快速變化的情況下,這種時間優勢能夠幫助客戶更快地獲得產品驗證數據,加速產品上市。

l 尺寸優化:晶圓級技術需要在基板上方添加中介層,而EMIB則將硅橋嵌入基板,極大地提高了基板面積的利用率。同時,基板的尺寸與集成電路面板的格式相匹配,采用EMIB能夠在單個封裝中集成更多芯片,從而容納更多的工作負載。

l 供應鏈與產能:英特爾擁有成熟的供應鏈和充足的產能,確保了EMIB能夠滿足客戶對先進封裝解決方案的需求。

先進封裝技術的未來發展

l 英特爾正在研發120×120毫米的超大封裝。【英特爾先進封裝:助力AI芯片高效集成的技術力量】

l 英特爾計劃在未來幾年內向市場推出玻璃基板(glass substrate)。玻璃基板可耐受更高的溫度,將變形(pattern distortion)減少50%,并具有極低的平面度,可改善光刻的聚焦深度(depth of focus),還達到了實現極緊密的層間互連疊加所需的尺寸穩定性。由于這些獨特的性能,玻璃基板上的互連密度有望提升10倍。此外,玻璃機械性能的改進實現了非常高的超大尺寸封裝良率。

此外,玻璃基板對更高溫度的耐受性,也讓芯片架構師能夠更靈活地設置電源傳輸和信號路由設計規則,因為它在更高溫度下的工作流程中,提供了無縫集成光互連器件和將電感器和電容器嵌入玻璃的能力。因此,采用玻璃基板可以達成更好的功率傳輸解決方案,同時以更低的功耗實現所需的高速信號傳輸,有助于讓整個行業更接近2030年在單個封裝內集成1萬億個晶體管的目標。【滿足更高算力需求,英特爾率先推出用于下一代先進封裝的玻璃基板】

評論