5G加速 聯電首推RFSOI 3D IC解決方案

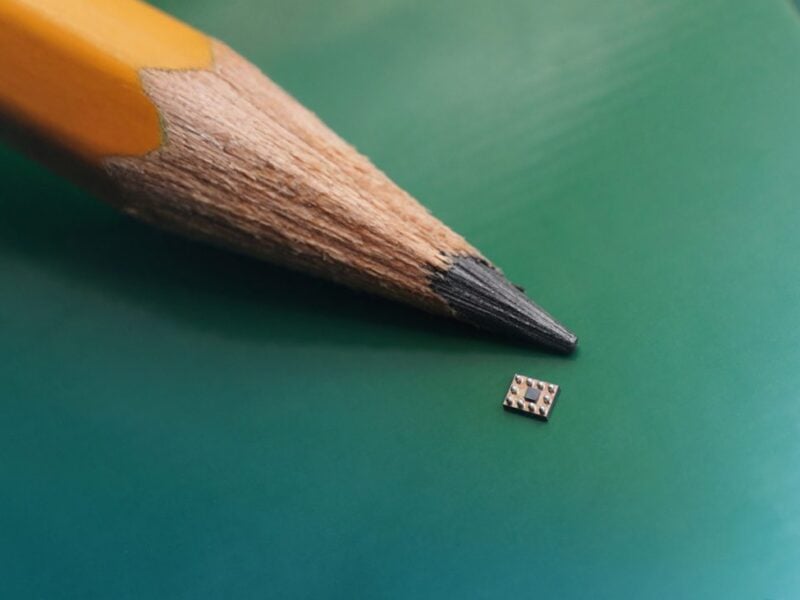

聯電昨(2)日所推出業界首項RFSOI 3D IC解決方案,此55奈米RFSOI制程平臺上所使用的硅堆棧技術,在不損耗射頻(RF)效能下,可將芯片尺寸縮小逾45%,聯電表示,此技術將應用于手機、物聯網和AR/VR,為加速5G世代鋪路,且該制程已獲得多項國際專利,準備投入量產。

聯電表示,RFSOI是用于低噪聲放大器、開關和天線調諧器等射頻芯片的晶圓制程。隨著新一代智能手機對頻段數量需求的不斷增長,聯電的RFSOI 3D IC解決方案,利用晶圓對晶圓的鍵合技術,并解決了芯片堆棧時常見的射頻干擾問題,將裝置中傳輸和接收數據的關鍵組件,透過垂直堆棧芯片來減少面積,以解決在裝置中為整合更多射頻前端模塊帶來的挑戰。該制程已獲得多項國際專利,準備投入量產。

聯電指出,RFSOI解決方案系列從130到40奈米的制程技術,以8吋和12吋晶圓生產,目前已完成超500個產品設計定案,出貨量更高達380多億顆。

聯電技術開發處執行處長馬瑞吉(Raj Verma)表示,聯電領先業界以創新射頻前端模塊的3D IC技術打造最先進的解決方案,這項突破性技術不僅解決5G/6G智慧手機頻段需求增加所帶來的挑戰,更有助于在行動、物聯網和虛擬現實的裝置中,透過同時容納更多頻段來實現更快的數據傳輸。未來將持續開發如5G毫米波芯片堆棧技術的解決方案,以滿足客戶對射頻芯片的需求。

評論