使用大面積分析提升半導體制造的良率

l通過虛擬工藝開發(fā)工具加速半導體工藝熱點的識別

本文引用地址:http://www.104case.com/article/202403/455995.html這些技術可以節(jié)約芯片制造的成本、提升良率

設計規(guī)則檢查 (DRC) 技術用于芯片設計,可確保以較高的良率制造出所需器件。設計規(guī)則通常根據(jù)所使用設備和工藝技術的限制和變異性制定。DRC可確保設計符合制造要求,且不會導致芯片故障或DRC違規(guī)。常見的DRC規(guī)則包括最小寬度和間隔要求、偏差檢查以及其他規(guī)格,以避免在制造過程中出現(xiàn)短路、斷路、材料過量或其他器件故障。

在先進的半導體技術節(jié)點,DRC規(guī)則的數(shù)量增加和復雜性提升,導致傳統(tǒng)的2D DRC無法識別所有熱點和故障。2D DRC無法模擬或預測3D規(guī)則違規(guī),因此通常在開發(fā)晚期才能識別到3D故障。僅靠硅晶圓廠數(shù)據(jù)和測試宏來識別開發(fā)晚期的故障既耗時又昂貴。

泛林集團的SEMulator3D?虛擬制造平臺可用于進行半導體器件的3D建模和基于規(guī)則的量測,并用比硅晶圓實驗更快、更經濟的方式識別熱點(DRC違規(guī))和潛在故障。

大面積分析 (Large Area Analysis) 是半導體工程研發(fā)中的重要概念,指為了探索大面積芯片區(qū)域內潛在熱點的敏感性及其對下游工藝步驟的影響而進行的一系列實驗。經過精心設計的大面積分析可以幫助工程師用較少的實驗晶圓成本來開發(fā)出最佳的半導體工藝。

然而,大面積芯片區(qū)域潛在的工藝問題非常復雜,所以半導體設計和制造中的大面積分析(或實驗)空間并沒有被工程師充分挖掘。

本文中,我們將演示如何將SEMulator3D虛擬制造用于大面積分析,并通過在大面積模擬域中識別3D弱點展示我們的方法。

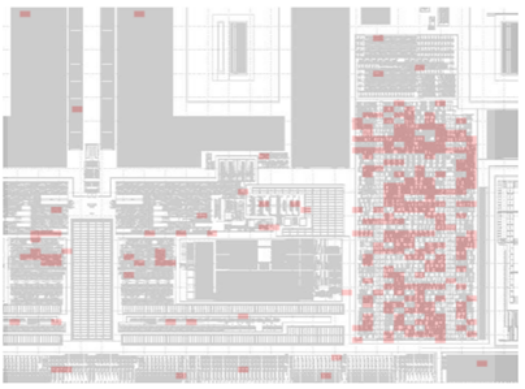

圖1:使用SEMulator3D進行大面積分析

大面積3D DRC集成流程

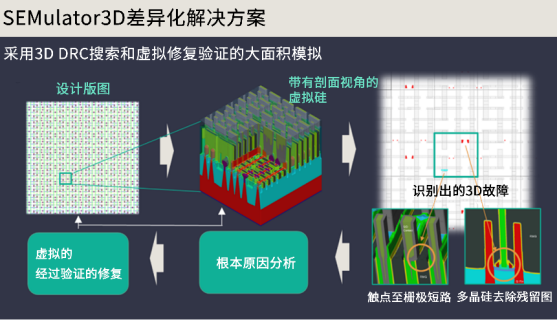

圖2是大面積分析3D DRC集成工藝圖。其中包含三個輸入值:SEMulator3D最佳已知方法工藝步驟模型、配置特定缺陷搜索標準的結構搜索宏和設計版圖。

通過3D預測性工藝建模,SEMulator3D可以使用這些輸入值來識別短路、斷路、材料過量等3D器件故障。此模擬的輸出值包括基于規(guī)則的量測、(搜索宏的)故障識別、以及缺陷圖的生成。

大面積分析工藝結束后,用戶可以查看整個大面積模擬域的測量結果。此外,還會生成包含潛在弱點的圖形數(shù)據(jù)系統(tǒng) (GDS) 版圖文件,供進一步參考。

我們可以看到大面積分析3D DRC集成工藝的每個輸出值,以及它們如何在半導體開發(fā)過程中加速熱點和故障識別。

圖2:大面積分析,3D DRC集成工藝圖

3D結構搜索中基于規(guī)則的量測

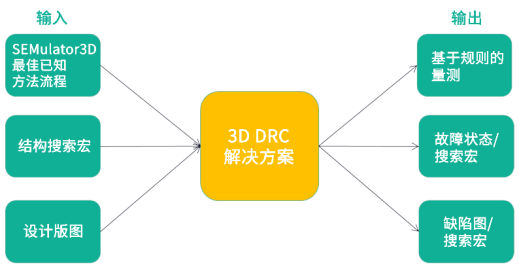

通過對3D結構進行基于規(guī)則的虛擬量測,SEMulator3D中的3D模型可用于搜索和驗證問題區(qū)域或熱點。一旦有違反規(guī)則,軟件會進行相應提示。而2D DRC工藝可能無法識別到所有這些違規(guī)——盡管使用簡單的2D DRC可以識別某些熱點,但由于2D DRC無法顯示沉積、刻蝕或其他光刻工藝的變異性,所以結果并不完整。

3D工藝建模包括工藝和結構信息,可用于突顯結構問題,比如絕緣距離太短、接觸區(qū)域重疊或其他限制良率的設計問題(如圖3)。在3D建模工藝中,可以建立幾何標準,以研究各種器件特征的最小/最大關鍵尺寸,以及材料接口問題和其他器件研究。這些信息可用于協(xié)助工藝/設計的共同優(yōu)化,并降低不可控性。通過在3D結構上進行虛擬且基于規(guī)則的量測,可以在開發(fā)早期、在硅晶圓廠數(shù)據(jù)和測試宏之前識別可能限制良率的故障。

圖3:3D工藝建模中識別的故障類型

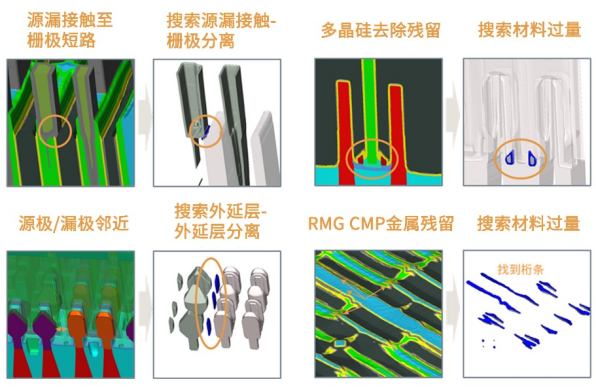

搜索宏和缺陷(熱點)圖

在SEMulator3D中,搜索宏可以識別大面積半導體區(qū)域內的違規(guī)或可能發(fā)生的器件故障。當搜索宏識別出故障時(使用基于規(guī)則的量測),會自動將結果輸出到一個GDS文件(如圖4),展示已識別故障的位置,該GDS文件包含在結構搜索工藝中識別的故障和缺陷。這些缺陷實際上是在3D結構中的,所以使用2D DRC方法通常無法識別它們。根據(jù)大面積研究中發(fā)現(xiàn)的缺陷類型,可能需要在SEMulator3D中進行工藝模型校準,以驗證預測準確性。理論上,識別意外缺陷不需要先進的校準。

圖4:大面積分析模擬的GDS文件,故障區(qū)域用紅色標記

結論

在不需要晶圓實驗的情況下識別工藝熱點非常有價值:這不僅可以節(jié)省晶圓和掩膜成本,更重要的是,可以加速技術開發(fā)中的良率提升。

在最近使用SEMulator3D的項目中,大面積分析解決方案在開發(fā)早期識別出多個掩膜缺陷。其中,兩個缺陷已經得到修正,并購買了新的掩膜。如果沒有使用虛擬工藝開發(fā)工具,這種掩膜故障識別可能花費數(shù)月時間、數(shù)次試樣的測試。

隨著半導體技術的進步,大面積分析技術可以預防、探測和修復熱點,從而將系統(tǒng)性、隨機性和參數(shù)缺陷數(shù)量降至最低,并最終提高良率。對希望按時交付新半導體產品的企業(yè)來說,大面積分析用于探究制造可行性將成為成功的關鍵因素。

評論