英特爾展示全球首款基于UCIe連接的Chiplet CPU

英特爾 CEO 帕特·基辛格(Pat Gelsinger)在 Innovation 2023 大會上展示了全球首款基于 UCIe 連接的 Chiplet(小芯片)處理器,該芯片采用 Intel 3 工藝節點上制造的 Intel UCIe IP 芯片,與在臺積電 N3E 節點上制造的 Synopsys UCIe IP 芯片配對。兩個 Chiplet 通過英特爾的 EMIB 接口進行通信。

本文引用地址:http://www.104case.com/article/202309/450802.htm通用 Chiplet Interconnect Express(UCIe)接口得到了眾多行業巨頭的支持,例如英特爾、AMD、Arm、英偉達、臺積電和三星以及其他 120 家公司。該互連設計旨在通過開源設計標準化 Chiplet 之間的芯片間互連,從而降低成本并培育更廣泛的經過驗證的 Chiplet 生態系統。

當今的多 Chiplet 封裝使用專有接口和協議相互通信,這使得廣泛采用第三方 Chiplet 成為一項艱巨的任務。UCIe 的目標是創建一個具有標準化接口的生態系統,以便有一天芯片制造商能夠簡單地從其他設計人員那里選擇 Chiplet,并以最少的設計和驗證工作將它們融入到新設計中。

UCIe 聯盟于 2022 年成立,已經獲得了芯片制造行業的廣泛支持。聯盟已經相繼推出了 UCIe 1.0、1.1 規范。該聯盟制定了非常激進的性能和面積目標,將目標市場分為兩個廣泛的范圍,采用標準 2D 封裝技術和更先進的 2.5D 技術(EMIB、CoWoS 等)。先進的封裝選項可提供更高的帶寬和密度。

英特爾基于 Chiplet 的處理器,如 Sapphire Rapids 和新發布的 Meteor Lake,目前使用專有接口和協議進行 Chiplet 之間的通信,但英特爾已宣布將在其下一代 Arrow Lake 消費級處理器之后使用 UCIe 接口。AMD 和英偉達也在致力于自己的計劃,但還沒有展示可用的硅芯片。

作為一家長期領先的半導體企業,以 CPU 而聞名天下的廠商,英特爾在處理器方面的進展尤其值得關注。在本次大會上,英特爾也的確帶來了全面的展示,英特爾的 PC 芯片從此也開始全面進入 AI 時代。

基辛格表示:「人工智能將從根本上改變、重塑和重構 PC 體驗,通過云和 PC 協同工作的力量釋放個人生產力和創造力。為此,英特爾正在開創人工智能電腦的新時代。」代號為 Meteor Lake 的 Intel Core Ultra 處理器,正是英特爾實現上述目標的一個重要倚仗。

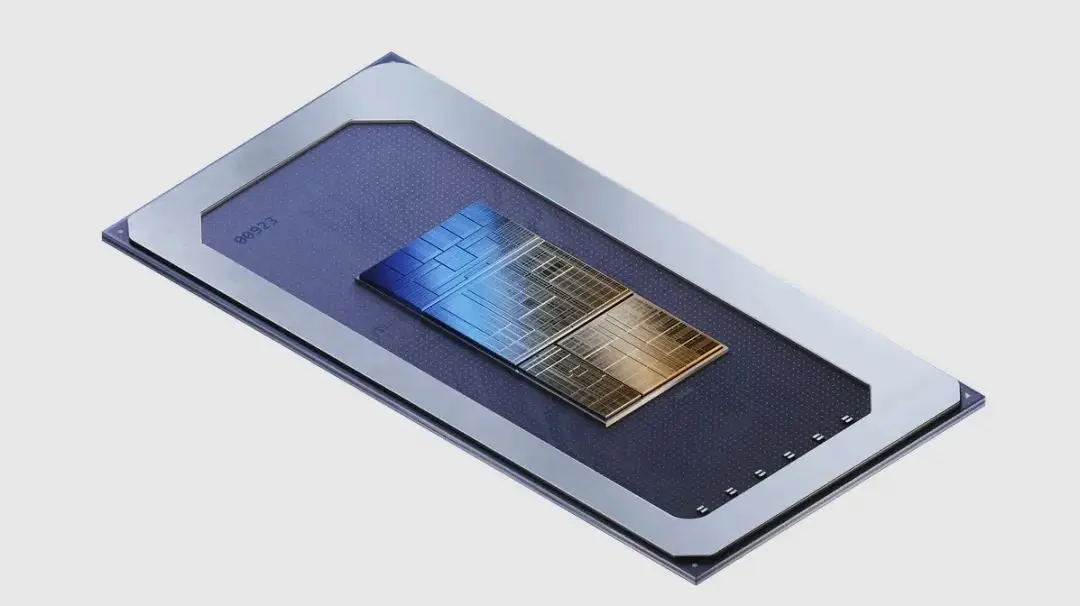

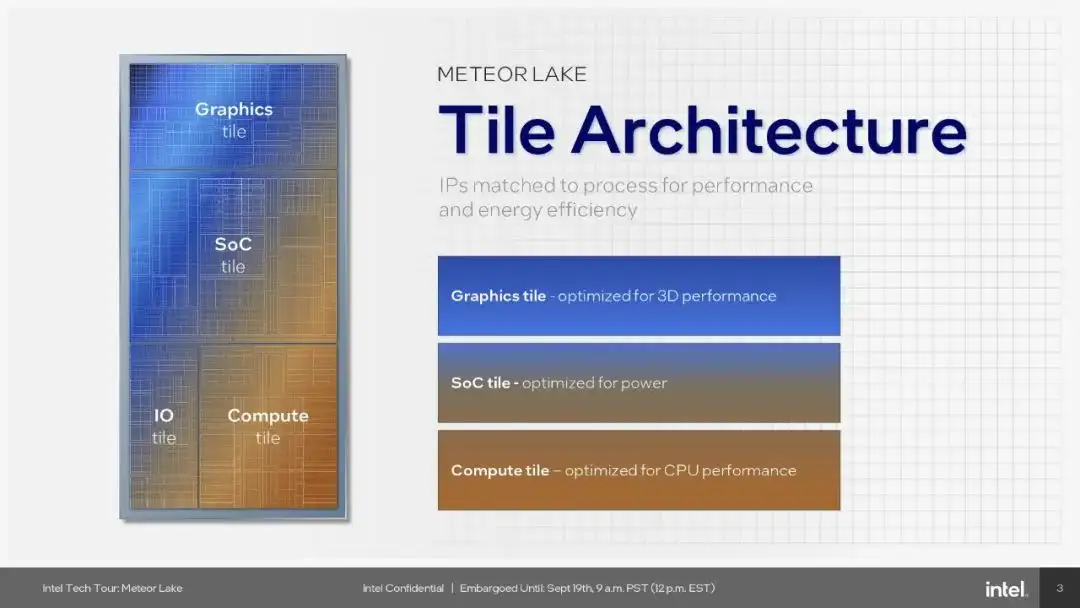

在英特爾看來,Core Ultra 代表了英特爾客戶端處理器路線圖的一個轉折點,因為它是第一個由 Foveros 封裝技術(英特爾的 3D 封裝技術)支持的客戶端 Chiplet 設計,還采用了 EUV 光刻技術。從設計上看,芯片內部包含了 computing tile、graphics tile 和 SoC tile 和 I/O tile 四個部分。其中,computing tile 是基于 Intel 4 工藝打造,graphics tile 是基于臺積電的 5nm 打造,SoC tile 則采用臺積電的 6nm 打造,這正是 Chiplet 精神的體現。值得一提的是,這個芯片的 Soc tile 上還集成了英特爾首個 NPU。

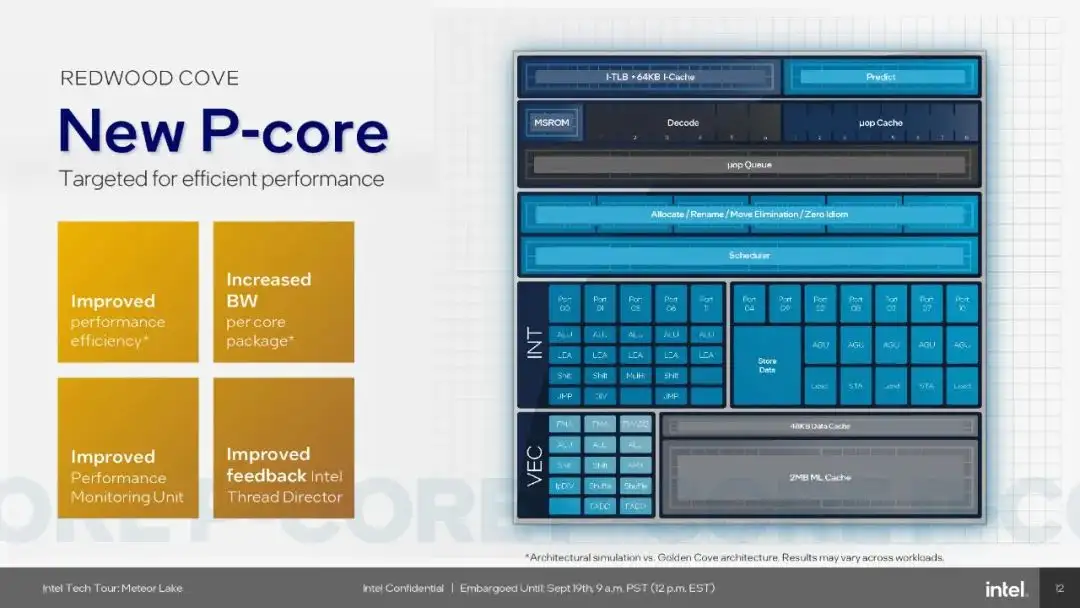

具體到芯片設計細節上。據透露,該芯片的 couputing tile 中有一對新的核心,一個名為 Redwood Cove 的 P 核心和一個名為 Crestmont 的新 E 核心。其中,新的 P 核心是英特爾第 12 代核心 (Raptor Lake) 處理器中之前的 Golden Cove 核心的直接繼承者,通過新的 Redwood Cove 核心,英特爾在芯處理器上帶來了不小的 IPC 提升。

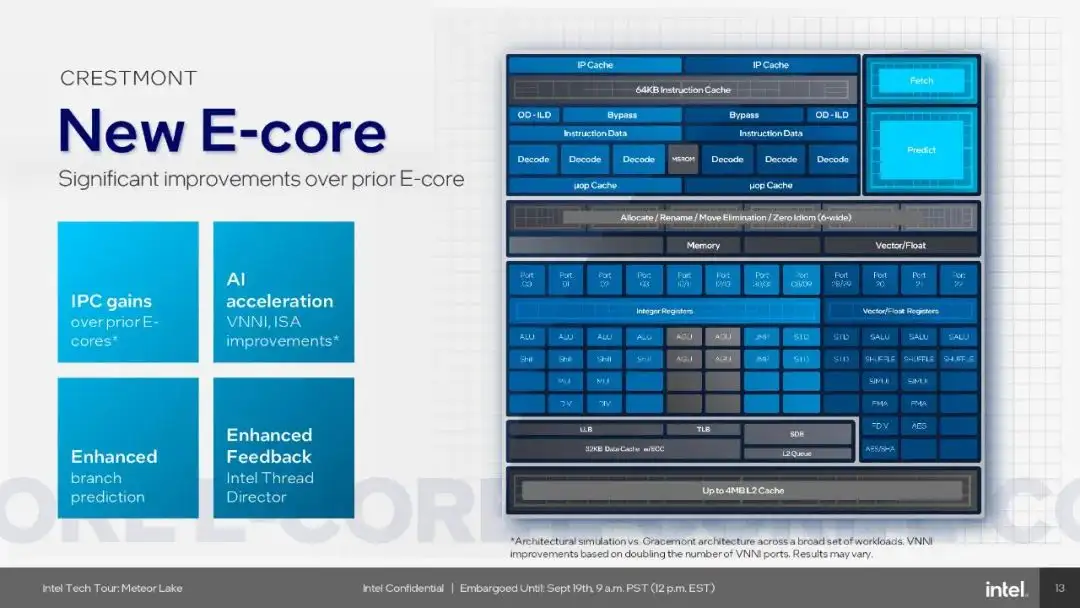

至于 E 核心,據報道,通過矢量神經網絡指令 (VNNI),該核心保持基于 CPU 的 AI 加速。而與 P-Core 一樣,E-Core 也受益于增強的 Thread Director 反饋,它提供了更好的粒度控制和優化。

來到 SoC tiles 上,據介紹,通過在硅片上實施片上網絡 (NOC),英特爾擺脫了網狀路由的舊有限制。這不僅僅是為了讓數據通道更快,而是旨在實現對內存的更智能、更節能的訪問。在利用 EMIB 和 2D 縮放后,數據路徑會短得多,從而減少功耗,但較短的電線也有助于減少總體延遲損失。

如前面所說,在這個 SoC tile 上,還有一個全功能神經處理單元 (NPU),這是英特爾面向客戶端處理器的首個 NPU,得益于這個模塊,英特爾能夠直接將 AI 功能引入到客戶端芯片上,且因為其與 OpenVINO 等標準化程序接口兼容,這就使得在開發的時候能夠給相關人員帶來便利。據介紹,這個 NPU 由兩個神經計算引擎組成,它們可以協作完成單個任務,也可以獨立運行。而這些神經計算引擎的則主要包括了兩個組件:推理 pipeline 和 SHAVE DSP。

評論