imec首度展示晶背供電邏輯IC布線方案 推動2D/3D IC升級

比利時微電子研究中心(imec)于本周舉行的2022年IEEE國際超大規模集成電路技術研討會(VLSI Symposium),首度展示從晶背供電的邏輯IC布線方案,利用奈米硅穿孔(nTSV)結構,將晶圓正面的組件連接到埋入式電源軌(buried power rail)上。微縮化的鰭式場效晶體管(FinFET)透過這些埋入式電源軌(BPR)實現互連,性能不受晶背制程影響。

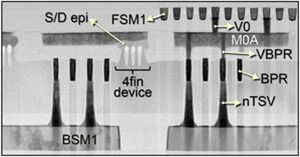

FinFET微縮組件透過奈米硅穿孔(nTSV)與埋入式電源軌(BPR)連接至晶圓背面,與晶圓正面連接則利用埋入式電源軌、通孔對電源軌(via to BPR;VBPR)以及電源超出主動區(metal over active;MOA)的結構設計。

這套先進的布線方案能分離電源線與訊號線的配置,推動2nm以下邏輯芯片持續微縮,還能增強供電效能,進而提升系統性能。此外,imec也在晶圓背面導入了采用2.5D金屬—絕緣體—金屬(MIM)結構的電容,展現更佳的芯片效能。

晶背供電設計能分離邏輯IC的電源供應網絡與訊號線,進而減緩后段制程布線壅塞的問題,還能帶來優化供電效能的好處。2019年imec首次提出這項技術,不同的制程方案也隨之出現。例如,在2021年VLSI技術研討會,imec首度展示晶背導線互連的實例,將奈米硅穿孔連接到位于晶圓正面的M1金屬層襯墊。

今年VLSI技術研討會,imec在其發表的論文中展示一套進階整合方案,透過埋入式電源軌,將FinFET微縮組件一齊連接到晶圓正面與背面,創下全球首例。imec的CMOS組件技術研究計劃主持人Naoto Horiguchi表示:「我們相信,從微縮組件與提升性能的角度來看,采用晶背供電設計并導入埋入式電源軌是最有可能實現晶背供電網絡的解決方案,這些電源軌在前段制程中埋入芯片,以局部布線的結構設計推動芯片微縮。」

他接著說明:「我們在開發測試芯片時,從晶圓正面定義埋入式電源軌的圖形,隨后將奈米硅穿孔連接到這些電源軌上,結果顯示FinFET組件性能不受晶背制程影響,這就包含接合目標晶圓與承載晶圓、薄化晶背以及制造深度長達320nm的奈米硅穿孔。奈米硅穿孔以垂直向與埋入式電源軌緊密接合,各穿孔的間距僅200nm,不占用標準單元尺寸,能確保組件繼續微縮至2nm以下。」

晶背供電設計可望從系統層面提升整體供電效能,尤其目前組件所需的功率密度持續攀升,供應電壓或IR壓降的問題也越來越嚴峻。imec的3D系統整合計劃VP Eric Beyne表示:「我們在2022 VLSI技術研討會上發表的一篇論文,在晶背制程中導入一顆2.5D柱狀MIM結構的去耦電容。透過這顆2.5D電容,電容密度因此提升了4~5倍,IR壓降現象與無電容(32.1%)及2D電容(23.5%)相比都來得低。這些分析結果來自一套經過實驗數據校正的IR壓降模擬架構。」

Eric Beyne總結:「我們的研究成果顯示晶圓背面具備高彈性的設計空間,還能訴諸全新的設計選擇,解決傳統2D芯片微縮的痛點。此外,我們也展示了一些3D系統級微縮技術的效能,在剝離承載晶圓時,以功能性晶圓取而代之,例如用于3D SOC邏輯組件堆棧的邏輯晶圓,而底層的晶粒可從晶背取得電源供應。」

評論