臺積電公布3納米光刻規劃及未來路線

臺積電昨天召開了第一次虛擬技術研討會,公布了3納米光刻及未來路線計劃。

本文引用地址:http://www.104case.com/article/202008/417553.htm過去幾年,臺積電已經與英特爾旗鼓相當,在半導體領域占據了領導地位。在今年年初英特爾宣布推遲其7納米工藝后,臺積電正抓住機會,以行業領導者的身份繼續“攻城略地”。

據臺積電高級副總裁米玉杰表示,該公司有計劃繼續提供有意義的節點改進,直到N3及以下。

總的來說,7納米得到了一系列產品系列的支持,而不僅僅是單一的芯片類型或類別,它貢獻了臺積電2020年第二季度36%的收入。

接下來,關于N5和N6節點的一些更新。根據臺積電的說法,N6比N5的邏輯密度提高了1.18倍。對于N5節點(與N7相比),收益更大:1.15倍的性能,或1.3倍的功耗改進,或1.8倍的邏輯密度改進。與N5相比,N5P預計將進一步提高1.05倍的性能或降低1.1倍的功耗。

臺積電今天披露的N4節點將降低掩膜層要求,并提供直接的遷移路徑。米玉杰沒有提供更多細節,說明N4提供了哪些改進,或者哪些特定客戶會遷移到該節點。預計在2021年第四季度進行風險生產,計劃在2022年進行量產。

至于N3,臺積電預計它將在2022年成為最新、最先進的節點。與N5相比,收益同樣不大,性能僅提升1.1-1.15倍,功耗提升1.25-1.3倍。這些增益是相對于N5而言的,而不是N5P。與7納米相比,N3在同樣的功率下,性能應該提高1.25倍-1.35倍,或者在同樣的性能下功耗降低1.55倍-1.6倍。請記住,在這些比較中,你看到的所有倍數都是假設一個理想化的晶體管,并不一定符合AMD、英特爾甚至英特爾實際制造的產品。制造商通常不會針對任何單一類別進行優化,而是利用所有三個類別中提供的一些改進。

臺積電轉向這些細分節點,提供多個相對類似的選項,其中一個原因可能是為客戶提供小規模迭代改進的選擇,并推出新產品,而不需要根據新的設計規則重新打造。有些人可能還記得,臺積電在多年前就推出了所謂的 "半節點",為那些想更快地利用小改進的代工客戶提供迭代步驟。半節點的命名方式已經不再使用,但這似乎是這個想法的概念基礎。如果你打造一個5納米CPU,不想為3納米打造一個新的部件,你可以遷移到5NP或可能的N4,在成本和密度上實現一些改進,并將新節點轉變的成本分攤到幾年內。

N3將繼續使用FinFET鰭式場效晶體管,而不是過渡到GAA環繞式結構場效晶體管。這與三星不同,三星已經表示要在3納米節點使用GAA。不過,三星似乎在自己的7納米坡道上遇到了一些問題,所以這些計劃有可能會發生變化。

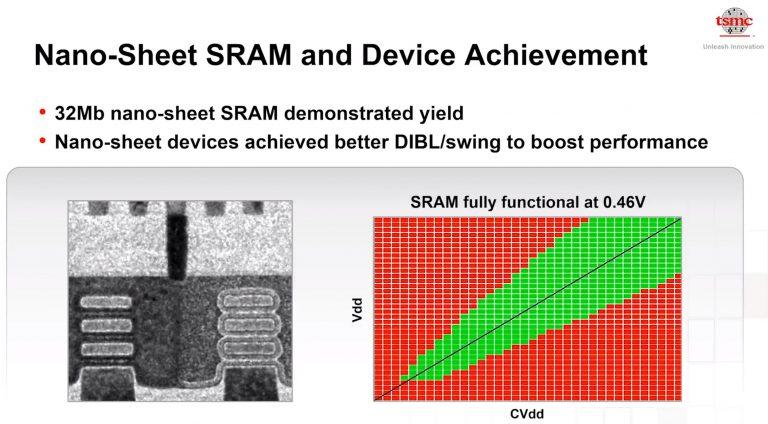

臺積電繼續致力于納米片和納米線的研究,并展示了一種32Mb納米片SRAM,在0.46v下仍可運行。上圖中的堆疊 "片 "顯示了從基于FinFET的方法的過渡,不過臺積電沒有計劃在2022年之前將這項技術商業化。

臺積電還討論了它所取得的一些具體的技術成就,不過并不是所有這些成就都與部署在某個節點上有關。它已經成功地在后端(BEOL)28納米CMOS中部署了一個碳納米管功率柵極器件,并成功演示了一個空氣隔板,以降低10%的柵極到漏極電容。它還制定了提供更好的通阻和電路RC延遲的路線圖。

其中一些單獨的改進帶來了令人印象深刻的收益,比如據稱通阻降低了50%,。

考慮到臺積電進入大批量生產和公司推出產品之間的滯后,臺積電為其即將到來的節點給出的特性將對AMD、英偉達、高通和蘋果在2023到2024年之前推向市場的芯片類型產生有意義的影響。

總的來說,臺積電發出的信號是,我們可以期待有意義地改善功耗和晶體管密度,但每晶體管層面的性能只會有小幅提升。從臺積電的16FF到7納米節點的性能提升不會從N7復制到N3。這并不意味著硅設計人員不會找到提高性能的方法,這只是意味著他們可能不得不通過進一步提高使用晶體管的效率或設計芯片的類型來實現。最近的一項研究表明,制造商往往難以實現這些改進,而是依賴于每個連續制造節點所能帶來的收益。由于密度逐代提升強勁,但功率和性能的改善幅度較小,預計將有更多企業轉向先進的封裝和分解,希望通過更高的效率獲得更多的回旋余地。

芯片是由晶體管和內部互連構成,晶體管相當于開關。利用銅布線實現晶體管頂部的互連,這些布線使電信號實現在晶體管間的傳遞。芯片有10到15層銅互連,一般來說,第二金屬層M2的間距最窄,因此,芯片技術節點名稱就是根據最窄節距定義,通常是最合適的布線的間距。采用光刻技術后,節點名稱和規格不再與M2間距一致,而且不同廠商的定義也不一樣。現在的芯片制造節點名稱更像是一個市場化的數字,然而,每一個節點和上一個節點相比都有所改進。

評論