7nm處理器是極限么?

硅芯片工藝自問世以來,一直遵循摩爾定律迅速發(fā)展。但摩爾定律畢竟不是真正的物理定律,而更多是對現(xiàn)象的一種推測或解釋,我們也不可能期望半導(dǎo)體工藝可以永遠(yuǎn)跟隨著摩爾定律所說發(fā)展下去。從現(xiàn)在來看,10nm工藝是能夠?qū)崿F(xiàn)的,7nm也有了一定的技術(shù)支撐,而5nm則是現(xiàn)有半導(dǎo)體工藝的物理極限。

本文引用地址:http://www.104case.com/article/201710/366211.htm所以,為了盡可能地延續(xù)摩爾定律,科研人員也在想盡辦法,比如尋求硅的替代材料,以繼續(xù)提高芯片的集成度和性能。

10年前我們覺得65nm工藝是極限,因為到了65nm節(jié)點二氧化硅絕緣層漏電已經(jīng)不可容忍。所以工業(yè)界搞出了HKMG,用high-k介質(zhì)取代了二氧化硅,傳統(tǒng)的多晶硅-二氧化硅-單晶硅結(jié)構(gòu)變成了金屬-highK-單晶硅結(jié)構(gòu)。

5年前我們覺得22nm工藝是極限,因為到了22nm溝道關(guān)斷漏電已經(jīng)不可容忍。所以工業(yè)界搞出了finfet和FD-SOI,前者用立體結(jié)構(gòu)取代平面器件來加強柵極的控制能力,后者用氧化埋層來減小漏電。

現(xiàn)在我們覺得7nm工藝是極限,因為到了7nm節(jié)點即使是finfet也不足以在保證性能的同時抑制漏電。所以工業(yè)界用砷化銦鎵取代了單晶硅溝道來提高器件性能。

當(dāng)我們說工藝到了極限的時候,我們其實是在說在現(xiàn)有的結(jié)構(gòu)、材料和設(shè)備下到了極限。然而每次遇到瓶頸的時候,工業(yè)界都會引入新的材料或結(jié)構(gòu)來克服傳統(tǒng)工藝的局限性。當(dāng)然這里面的代價也是驚人的,每一代工藝的復(fù)雜性和成本都在上升,現(xiàn)在還能夠支持最先進(jìn)工藝制造的廠商已經(jīng)不多了。有限的這幾家都在努力中:Intel、臺積電、三星和GlobalFoundries。

7nm工藝是極限了嗎?

適用了20余年的摩爾定律近年逐漸有了失靈的跡象。從芯片的制造來看,7nm就是硅材料芯片的物理極限。

在長達(dá)40多年的時間里,摩爾定律始終是IT界的鐵律。然而進(jìn)入21世紀(jì)以來,摩爾定律似乎出現(xiàn)了“放緩”的跡象。

隨著芯片技術(shù)的進(jìn)一步發(fā)展,摩爾定律逐漸遇到物理法則的限制。業(yè)界普遍認(rèn)為,7納米是硅晶體管的一道坎,一旦過了這個節(jié)點,就會遇到問題。因為一旦硅晶體管的柵極小于7納米,電子就可以在不同的晶體管之間流動,這種現(xiàn)象被稱為量子穿隧效應(yīng)(Quantum Tunneling),它意味著晶體管可能會在原本應(yīng)該是關(guān)閉的狀態(tài)下意外打開。

但即使是7納米以上的晶體管,也依然面臨從理論向?qū)嶋H跨越的難題。

7納米制程節(jié)點將是半導(dǎo)體廠推進(jìn)摩爾定律(Moore’s Law)的下一重要關(guān)卡。半導(dǎo)體進(jìn)入7納米節(jié)點后,前段與后段制程皆將面臨更嚴(yán)峻的挑戰(zhàn),半導(dǎo)體廠已加緊研發(fā)新的元件設(shè)計架構(gòu),以及金屬導(dǎo)線等材料,期兼顧尺寸、功耗及運算效能表現(xiàn)。

現(xiàn)在的CPU內(nèi)集成了以億為單位的晶體管,這種晶體管由源極、漏極和位于他們之間的柵極所組成,電流從源極流入漏極,柵極則起到控制電流通斷的作用。

而所謂的XX nm其實指的是,CPU的上形成的互補氧化物金屬半導(dǎo)體場效應(yīng)晶體管柵極的寬度,也被稱為柵長。

縮短晶體管柵極的長度可以使CPU集成更多的晶體管或者有效減少晶體管的面積和功耗,并削減CPU的硅片成本。正是因此,CPU生產(chǎn)廠商不遺余力地減小晶體管柵極寬度,以提高在單位面積上所集成的晶體管數(shù)量。不過這種做法也會使電子移動的距離縮短,容易導(dǎo)致晶體管內(nèi)部電子自發(fā)通過晶體管通道的硅底板進(jìn)行的從負(fù)極流向正極的運動,也就是漏電。而且隨著芯片中晶體管數(shù)量增加,原本僅數(shù)個原子層厚的二氧化硅絕緣層會變得更薄進(jìn)而導(dǎo)致泄漏更多電子,隨后泄漏的電流又增加了芯片額外的功耗。

為了解決漏電問題,Intel、IBM等公司可謂八仙過海,各顯神通。比如Intel在其制造工藝中融合了高介電薄膜和金屬門集成電路以解決漏電問題;IBM開發(fā)出SOI技術(shù)——在在源極和漏極埋下一層強電介質(zhì)膜來解決漏電問題;此外,還有鰭式場效電晶體技術(shù)——借由增加絕緣層的表面積來增加電容值,降低漏電流以達(dá)到防止發(fā)生電子躍遷的目的。。.。。.

上述做法在柵長大于7nm的時候一定程度上能有效解決漏電問題。不過,在采用現(xiàn)有芯片材料的基礎(chǔ)上,晶體管柵長一旦低于7nm,晶體管中的電子就很容易產(chǎn)生隧穿效應(yīng),為芯片的制造帶來巨大的挑戰(zhàn)。針對這一問題,尋找新的材料來替代硅制作7nm以下的晶體管則是一個有效的解決之法。

石墨烯被視為是一種夢幻材料,它具有很強的導(dǎo)電性、可彎折、強度高,這些特性可以被應(yīng)用于各個領(lǐng)域中,甚至具有改變未來世界的潛力,也有不少人把它當(dāng)成是取代硅,成為未來的半導(dǎo)體材料。但是真正把它應(yīng)用于半導(dǎo)體領(lǐng)域,還需要克服不少的困難。

首先,通過前面我們可以知道,邏輯電路有“0”和“1”,也就是開和關(guān)兩種狀態(tài),而這就需要有“能隙”——電子攜帶電流之前必須躍過的能量跨欄。但是因為石墨烯本身的導(dǎo)電性能太好,它沒有能隙,也就是只能開,而不能關(guān),這樣是不能實現(xiàn)邏輯電路的。如果要利用石墨烯來制造半導(dǎo)體器件,那么我們還需要通過其他手段,在不破壞石墨烯本身特有的屬性下,在石墨烯上面植入一個能隙。目前已經(jīng)有不少針對這方面的研究,但要真正解決這個問題還需要相當(dāng)長的時間。

1nm那還只是個噱頭

美國勞倫斯•伯克利國家實驗室(Lawrence Berkeley NaTIonal Laboratory)的一個研究團(tuán)隊—已經(jīng)成功研制出柵極(晶體管內(nèi)的電流由柵極控制)僅長1納米的晶體管,號稱是有史以來最小的晶體管。這下很多人都不淡定了,媒體紛紛疾呼“摩爾定律沒戲唱了”。

我們來看看這個所謂的1nm。我們知道cmos技術(shù)中的晶體管是場效應(yīng)晶體管,是用一個柵控制一個導(dǎo)電溝道通斷來表示0和1的,柵和導(dǎo)電溝道中有一層絕緣電介質(zhì),柵加電壓,會在溝道處產(chǎn)生一個電場(但沒有電荷交換),該電場會改變溝道中的電子輸運性質(zhì),使得在溝道兩端加相同電壓,電子輸運性質(zhì)不同,電流不同,顯示出開關(guān)性。

導(dǎo)電溝道縮短過程中,電子的輸運特性會發(fā)生變化,這是電子的運動性質(zhì)決定的。而這個過程中對電流的調(diào)控越來越難,要么開態(tài)太小,要么關(guān)態(tài)太大,除此外還經(jīng)歷過柵介質(zhì)漏電等問題。

如果用單根的碳納米管作為柵,柵的寬度就是碳納米管寬度,但問題在于他的導(dǎo)電溝道沒有縮短,現(xiàn)有的場效應(yīng)晶體管柵完全覆蓋溝道的比較多(調(diào)控作用強),讓我們誤認(rèn)為柵的尺度就可以代表晶體管的特征尺度,那篇文章在這上面取了個巧,所以那個晶體管不一定就只有1nm。

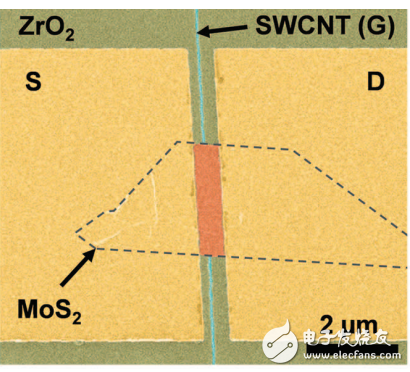

而且,本次外媒報道的勞倫斯伯克利國家實驗室將現(xiàn)有最精尖的晶體管制程從14nm縮減到了1nm,其晶體管就是由碳納米管摻雜二硫化鉬制作而成。不過這一技術(shù)成果僅僅處于實驗室技術(shù)突破的階段,目前還沒有商業(yè)化量產(chǎn)的能力。至于該項技術(shù)將來是否會成為主流商用技術(shù),還有待時間檢驗。

這僅僅是一項在實驗室中的技術(shù)突破,哪怕退一步說,該項技術(shù)已經(jīng)成熟且可以商業(yè)化,由于其在商業(yè)化上的難度遠(yuǎn)遠(yuǎn)大于Intel正在研發(fā)的10nm制造工藝——其成本將高昂地?zé)o以復(fù)加,這會使采用該技術(shù)生產(chǎn)的芯片價格居高不下。

推薦閱讀:

臺積電預(yù)告2017年第二季10納米芯片將會量產(chǎn),7納米制程的量產(chǎn)時間點則將落在2018年上半。反觀英特爾(Intel),其10納米制程量產(chǎn)時間確定將延后到2017下半年。但英特爾高層強調(diào),7納米制程才是決勝關(guān)鍵,因為7納米的制程技術(shù)與材料將會有重大改變。

突破摩爾定律 臺積電17年要試產(chǎn)7nm芯片

評論