可配置電源管理ASIC--當今的系統黏合劑

上個世紀,在數字化思維主導設計領域時,系統是標準處理器,ASSP,模擬電路和黏合邏輯的混合物。“黏合邏輯”是通過小型和中型集成電路|0">集成電路把不同數字芯片的協議和總線連在一起。為了降低成本實現一體化,“黏合邏輯”曾經風靡整個ASIC業。

如今,整個數字系統發展到深亞微米(DSM)半導體階段,“黏合邏輯”也慢慢退出了系統設計應用。但是“黏合邏輯”真的過時了嗎?答案因人而異。現在,對于數字“黏合邏輯”的需求不如以前那么強烈,但是模擬“黏合功能”卻在增長。

復合信號ASIC—今天的“系統膠連”

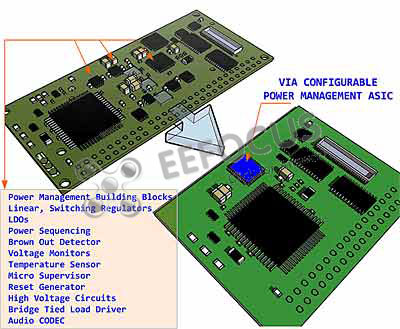

現在的系統有許多模擬功能,但是卻并不適合90和65納米硅芯片應用。這些系統需要多個電源層,若干電壓等級,電源的排序,睡眠模式功耗,高電壓LED驅動器,高質量音頻處理器以及這些功能的智能控制。系統級芯片數字化解決方案的增長導致我們需要復合信號集成電路,囊括了諸多為了節約成本,提高性能和集成的模擬功能。如圖1所示:

|

便攜式電子設備可能包括廣泛的電源電壓:用于數字集成電路的1.8V和3.3V電壓,用于鋰離子電池的4.2V電壓,用于傳統接口的5V電壓,用于LED背光的36V電壓,單獨的用于敏感模擬電路的電壓以及用于電機控制的高電壓。根據每個功率源的要求,設計師們選擇不同的電源轉換拓撲結構,其中包括線性,開關以及低壓降穩壓器。

不僅是調節器的純粹數量在增加,這些系統往往有復雜的電源排序要求,每個供應源相互之間在電源開關,睡眠和降低的操作模式時的開啟和關閉需要精確的控制。通常這些供應源不僅僅是簡單的打開,而需要電源電壓的斜升或斜降行為,從而增加了電源管理系統的額外的復雜性。在設備的電源管理設計中,隨著調壓器相互之間的正確排序,系統復位信號,振蕩器開啟和PLL穩定時間必須考慮進去。

一個電源管理系統集成了多種電源轉換拓撲結構,數字排序邏輯,控制電源管理功能的數字通訊,模擬電壓以及電流測量;不變性記憶器用來存儲電壓設置點,排列順序,序列周期和工廠校準數據。這些電源管理資源消耗了了許多電路板空間,需要多位包裝,并加入到組裝成本中,使其成為電源管理集成電路的理想候選。這些專用集成電路建立在混合信號處理的基礎上,因此相關功能不能與電源管理正常聯系,比如音頻處理,蜂鳴器驅動器和馬達控制,在設備中成為內含物的選擇器件。對于PMIC ASIC來說,負責集成和控制許多IP模塊很平常。功能如表1:

表1 PMIC 電源管理集成電路功能

線性調節器 電機控制

轉換器 音頻揚聲器驅動

低壓降穩壓器 自定義數字邏輯

發光二極管升壓穩壓器 電源排序

電池管理-充電,監視 復位發生器

LED驅動 電壓監視器

LCD電壓發生器 電流監視器

電壓轉換器 風扇控制

音頻處理 溫度傳感器

非易失性存儲器 欠壓檢測器

可配置電源管理集成電路

所有的模擬和電源管理“膠連”的進入讓一個單一設備實現了整合,提高了側尋性能,降低了整個系統的成本。然而,全定制的電源管理IC開發一向昂貴,進入市場緩慢,并且有很大的風險。

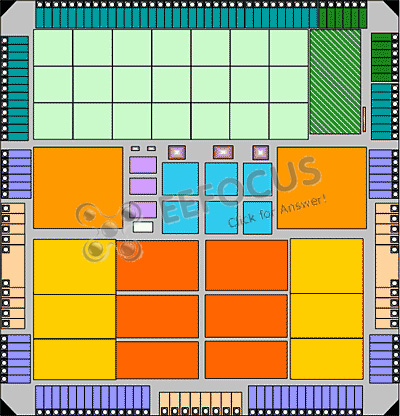

可配置陣列技術(VCA)的發展產生了硅驗證的電源管理ASIC的解決方案,通過一個單一的遮罩層的變化來配置和定制特定的應用。一個VCA在ASIC模塊上集成了硅驗證模擬化,數字化和內存資源。然后這些資源由整體的路由結構所覆蓋。包含這些VCA的晶片經過特殊處理和鑄造,所有的模擬和數字資源可相互聯系并由一個遮罩層來配置。由于只有一個遮罩層鑄造加工,制造成本大大降低,制造時間從幾個月到幾周,硅驗證的IP和互聯路的使用大大降低了風險。

|

圖2顯示了一個可配置的PMIC和其組成部分 |

表 2 適合電源管理應用的可配置ASIC的性能

3V至50V操作

15750 個ASIC門

21,500位的RAM

1000 × 8電可擦除只讀存儲器,20年的數據保存能力,100K的寫入周期

44個可配置數字I / O

12個20V的運算放大器與資源

12個3.3V的運算放大器與資源

6個電源管理單元

2個調節器

2個10位,1MSPS的DAC

42個可配置的模擬I / O

3.3V的獨立模擬電源

20V的獨立模擬電源

設計一個可配置電源管理集成電路(PMIC)

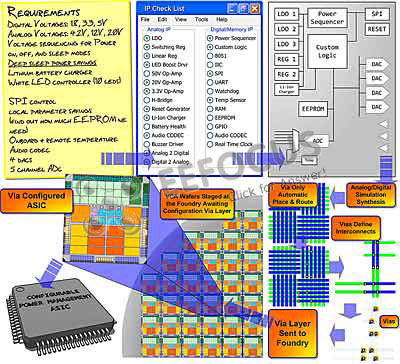

在可配置ASIC中制定一個綜合的電源管理方案遵循圖3的流程,從確定系統所需電壓范圍開始,每個區域所需的工作和睡眠模式的電流以及電源電壓的次序。PMIC的設計目的是獲取模擬圖表和數字硬件描述語言。高級別的設計用來

模擬確認設備操作。在傳統的全定制ASIC設計流程中,下一步將是艱苦的,昂貴的,容易出錯的晶體管布局,布局需要把設計轉化到具體的硅片上。在可配置流程中,HDL格式的數字設計綜合成Verilog(目前應用最為廣泛的硬件描述語言),在門級Verliog中,軟件通常把來自模擬圖表的SPICE表進行轉換。然后把模擬和數字Verliog網結合起來并提交給自動布局布線工具,通過全局路由結構來自動配置設備。

和全定制電源管理IC設計的數月相比,混合信號自動布局布線過程完全配置設備僅僅數天。在全局路由金屬層中,自動布局布線工具的輸出是掩模層的一個GDSII代表。和一個全定制設計來說需要20多個層相比,這個路由層發送到鑄造只需構造一個掩模層,從而大大減少了構造費用,使得原型從數月到數周成為可能。

|

圖3 可配置電源管理ASIC設計流程 |

可配置ASIC供應商給設計者們提供了集成于可配置ASIC的硅驗證的電源管理和混合信號IP模塊。對于集成電路設計來講,“無全定制布局需要”的方法導致了低成本,快速發展和更安全的設計流程。因此,設計團隊可以解決如今產品所需的充滿挑戰性的和不斷變化的電源管理解決方案。

作者簡介:

Reid Wender,應用工程師主管,2005年加入Triad半導體。之前,他是工程方面的副總裁,任職于QuVIs的半導體部門。他有20年的ASIC設計和項目管理經驗,包括Nextwave Silicon, ASIC International, Philips, 和IBM這些公司,并擁有田納西大學的電子工程學士學位。

評論