臺積電:7nm工藝已簽下20多個合同

臺積電(TSMC)在美國奧斯汀舉行的“Collaborating to Enable Design with the Latest Processors and FinFET Processes, including 7nm”(由美國新思科技、英國ARM和臺積電于6月6日聯合舉辦)上,介紹了采用10nm FinFET及7nm FinFET工藝的設計和生產進展情況。演講人跟上年一樣。

本文引用地址:http://www.104case.com/article/201606/292488.htm

(設計暨技術平臺副處長)

初次使用三重曝光的10nm工藝,第一款芯片已于2016年第一季度送廠生產(設計完成)。預計10nm工藝的量產將于2016年內開始。ARM于上周(5月30日)發布了利用10nm工藝制造的瞄準智能手機SoC的CPU內核“ARM Cortex-A73”和GPU內核“ARM Mali-G71”(參閱本站報道2),當時宣布:配備集成有這些內核的SoC的智能手機將于2017年上市。

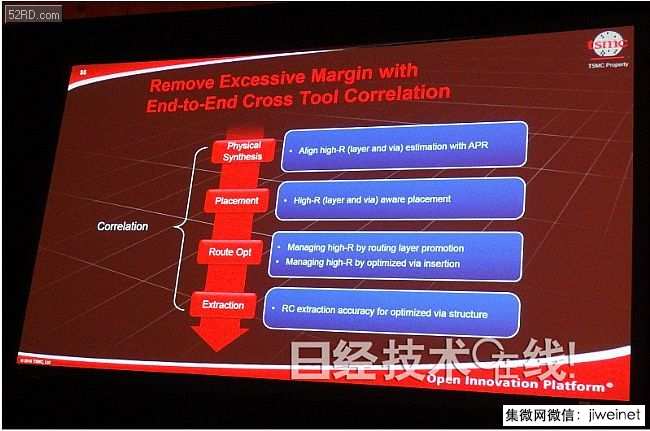

可以考慮每層各異的布線電阻及過孔電阻的設計流程

至于7nm工藝,Willy Chen表示“已簽訂了20多個合同”。已有用戶開始設計,將于2017年下半年送廠生產。7nm工藝的量產將于2018年開始。據Willy Chen介紹,7nm工藝與10nm工藝相比,邏輯集成度將提高60%,性能和耗電量將改善30~40%。另外,Willy Chen表示,希望利用該工藝不僅生產智能手機,還生產HPC(High Performance Computing)的芯片。

雖然有人預測7nm工藝將使用四重曝光,不過現在看來可能跟10nm工藝一樣采用三重曝光。Willy Chen介紹說“10nm和7nm工藝的設計流程基本相同”,不過,7nm工藝有些地方需要注意,比如要想發揮高速工藝實力有三個要點。即:(1)牢固的時鐘網布設方法,(2)削減布線延遲,(3)更加整合的設計流程。

關于(1),既不采用傳統的時鐘樹,也不采用最近備受關注的網格狀結構,而將采用介于兩者之間的方法。關于(2)布線延遲,根據每個布線層單獨考慮電阻及考慮過孔電阻至關重要。“僅根據布線長度來確定布線延遲已經行不通”(Willy Chen)。關于(3),則需要可以考慮每層各異的布線電阻及過孔電阻的設計流程。

評論