調試設計:芯片設計中必不可少之舉

在測試中,目的是要盡快確定芯片是否以較高的穩定性正常工作,而不是絕對的穩定性。現在芯片設計團隊普遍認識到,這需要在芯片上添加DFT(可測試設計)電路。第三方工具和IP (知識產權)企業可幫助實現此目標。

本文引用地址:http://www.104case.com/article/193494.htm

而調試則完全不同了。調試的目的并不只是簡單地確定芯片出現了故障,而是要找出故障的原因。這種檢查并不限于在測試臺上的幾秒鐘,可能要持續數周時間。它并不是自動進行的,而是需要芯片設計團隊的參加。它出現在設計周期中的離散點上:在第一個芯片設計階段、在可靠性研究階段和現場故障分析階段。

根據這種情況,可以想象,良好的DFT 策略應能夠滿足芯片調試的需要,而且,實際上也往往是如此。隨著SoC(單片系統) 設計越來越復雜,一流的設計團隊表 示,他們將對支持調試而不是測試的電路提供更多的計劃、實現工作以及芯片面積。

“十年前在設計3層金屬層時,這并不是什么大問題,”Bay Microsystems 工程部的高級副總裁Tony Chiang說。“如果芯片有問題,應該直接研究金屬層來察看電路,而對于聚焦離子束系統則應該重新布線。現在,對于9層金屬層和0.2mm金屬間距,問題就不是

那么簡單了。必須將電路設計成具有從芯片外部能控制和能觀察的,而在成本和時間預算上不超出我們的目標。”

這種情況,簡單扼要地描述了調試設計界的情況。

技術概覽

調試與DFT并不是完全脫離的。Broadcom公司的測試開發工程高級總監Kris Hublitz舉例介紹說,Broadcom有一個由70多名工程師組成的公司級團隊,他們與公司其它的芯片設計團隊共同從事調試和測試。Hublitz再三宣稱DFT廠商LogicVision是Broadcom芯片調試策略的主要合作伙伴。

其他人也同意這種觀點。“調試設計與生產測試并不是毫無關系,” CSR (Cambridge Silicon Radio) 的副總裁David McCall說。“兩者的起點差不多。”

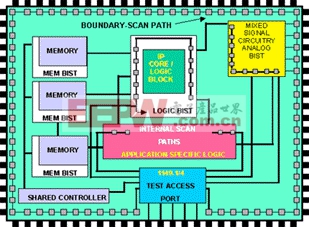

很多設計經理強調,這一起點就是探尋電路的能控性和能觀性。調試與生產測試相似,基本問題是將電路設置在一個已知的狀態,然后開始運行,觀察其行為。在中等規模的集成中,邊界掃描技術可有效地完成此任務。由于芯片內部狀態較少,可以全面地對其進行測試:將輸入通過已知的一系列狀態,對電路進行時鐘同步,然后觀察輸出。

隨著微處理器的出現,事情變得更加復雜了。微處理器有很多內部狀態,所以只將輸入施加給一個已知矢量并觀察輸出并不是特別有效。早期,業界嘗試了多種技術使微處理器實現可調試,從對寄存器間的每群邏輯進行掃描到依賴同類的跟蹤、斷點及微機用于進行軟件調試的單步函數等。將兩種方法結合起來才能起作用。

如今設計人員對SoC的數字部分使用相同的工具套件。另有一些技術用于混合信號的模擬電路。但沒有單獨一種方法可以囊括整個復雜的SoC。所以,調試的設計流程包括將系統分割成獨立的可調試模塊,對每個模塊實施一個調試策略,并將這些策略整合到一個完整芯片的方案中,使單個模塊的用戶接口相似并盡量減少電路需要的芯片資源。最后,設計師必須使用這些調試資源重新檢查,使完全集成的芯片的運行既可控制又可觀察,因為你不能只根據隔離功能模塊就能判斷某些問題。

數字SoC

最基本的SoC 形式是由簡單的往往是可編程的外設模塊和內存所包圍的CPU 核。多數情況下,CPU 核為第三方的IP,至少有一個內部調試內核的選項。軟件開發團隊經常強調這一點。此內核與標準的DFT 電路相結合,這種電路是設計團隊為外設所實施的,以實現能觀性和能控性來隔離故障。可以在CPU 核中應用這種調試內核,模擬核的非同步部分,以捕捉結果。通過讓CPU 讀寫外設寄存器,此內核也可模擬并觀察外設,通常允許設計師在可以處理的級別上確定掃描鏈中的故障。

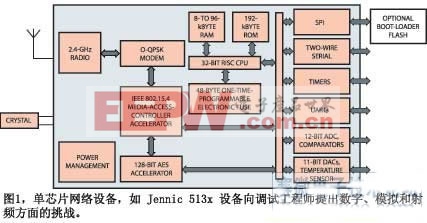

但如今并沒有多少這么簡單的SoC(圖 1)。更多的情況下,芯片有幾個或一群CPU 核和幾種不同的處理器內核。某些外部控制器非常復雜,只用CPU對其進行模擬來觀察結果,并不能對其有效診斷。還有多個時鐘域,它們之間通常彼此并不同步。這樣的芯片需要更有效的方法來調試。

在這種情況下,有幾種策略可用。Broadcom的Hublitz介紹的一種簡單方法是使所有主要功能模塊的輸入和輸出可以訪問芯片的針腳。這種方法需要大量的多路復用。在有大量I/O 和內存接口的設計中,在引入任何額外訪問進行調試之前,芯片針腳數已經限定了,設計人員必須復用針腳進行調試訪問。只將輸入輸出簡單引出每個復雜模塊,可能比將其在主CPU 核上執行更有用,設計師可能需要引出內部信號。

所有這些多路復用和輸入輸出傳送共同作用,可能并不太實際。而且,結果的額外互連會造成盡管所有模塊可從針腳進行實際訪問,但其訪問速度根本達不到要求。這是一個嚴重的問題。“我們必須要以全速測試電路,特別是模塊間的互連,”Hublitz 說。“這對于65 nm工藝的芯片更是如此。否則會產生芯片中的故障。”

Hublitz 強調,由ATE (自動測試設備) 支持的良好的DFT 策略,可極大地有助調試過程。“我們第一輪調試在ATE 系統上進行,”他說。“在我們清楚了芯片不會融化后,把它交給設計人員,與他們一起合作。”Hublitz同時表明,芯片可能會不斷地返回到 Broadcom的測試臺,以使 ATE 系統采集大量的數據或進行速度檢查。“自己內部有ATE 能力的真是很有用,”他表示。“我們有28 個系統,大概每季度就增加一個新的,主要是用于調試,調試新芯片是我們裝備設備最主要的目的。”

雖然有了ATE 系統,某些信號和 狀態還是不能通過探測卡的檢查。需要采用其它的策略:內部仿真和邏輯分析。有時,對模塊進行快速仿真和捕捉其行為的唯一有效途徑是將電路構建到模塊內部。據Chiang介紹,Bay將其網絡處理芯片組織成一串獨立的處理器,并廣泛應用這項技術。重要的模塊可以有其自己的調試內核,包括單步和斷點能力及跟蹤緩沖器實時捕捉

加速度計相關文章:加速度計原理

評論