基于Verilog的FPGA與USB 2.0高速接口設(shè)計(jì)

IDLE:當(dāng)寫(xiě)事件發(fā)生時(shí),轉(zhuǎn)到狀態(tài)1。

狀態(tài)1:指向IN FIFO,激活FIFOADR[1:O],轉(zhuǎn)向狀態(tài)2。

狀態(tài)2:如果FIFO滿標(biāo)志為“假”(FIFO不滿),則轉(zhuǎn)向狀態(tài)3;否則停留在狀態(tài)2。

狀態(tài)3:傳送總線驅(qū)動(dòng)數(shù)據(jù)。為一個(gè)IFCLK激活SLWR,轉(zhuǎn)向狀態(tài)4。

狀態(tài)4:如果有更多的數(shù)據(jù)要寫(xiě),則轉(zhuǎn)向狀態(tài)2;否則轉(zhuǎn)向IDLE。

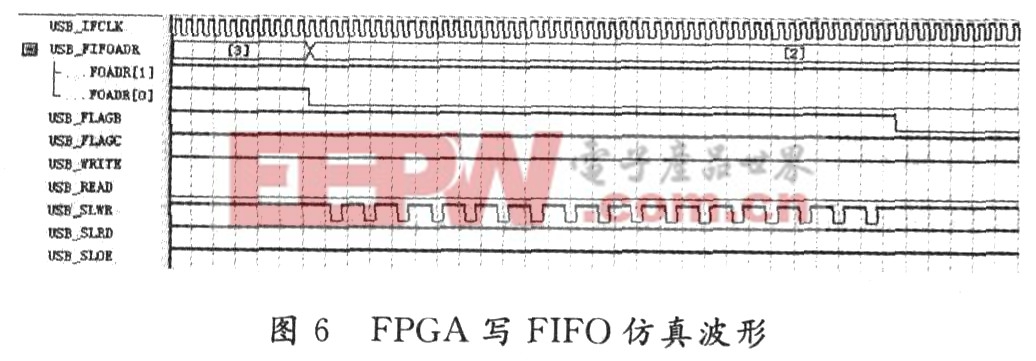

用QuartusⅡ進(jìn)行仿真驗(yàn)證,其仿真波形如圖6所示,在此過(guò)程中USB_SLWR信號(hào)很重要,經(jīng)分析可知,本狀態(tài)機(jī)實(shí)現(xiàn)的FIFO寫(xiě)控制信號(hào)完全正確。

3 實(shí)驗(yàn)結(jié)果

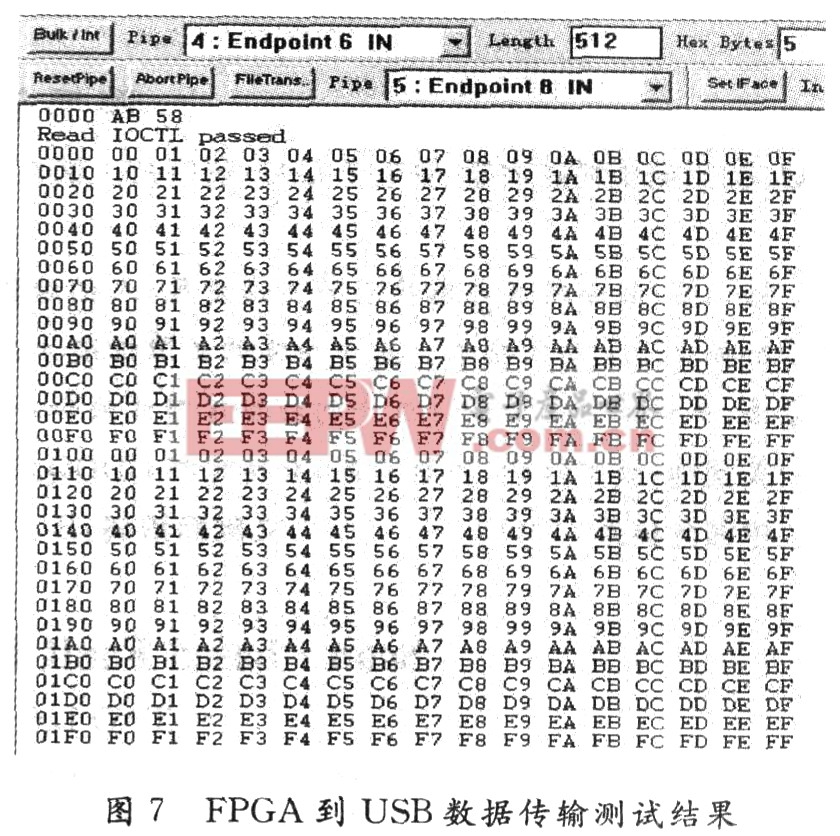

對(duì)傳輸?shù)臄?shù)據(jù)進(jìn)行驗(yàn)證,可通過(guò)FPGA編程生成O~255的數(shù)據(jù)傳送至CY7C68013的EP6端點(diǎn),連續(xù)傳送兩次,然后利用EZ一USB Control Panel軟件測(cè)試所接收到的數(shù)據(jù),測(cè)試結(jié)果如圖7所示,可以看出,數(shù)據(jù)傳輸準(zhǔn)確無(wú)誤。

4 結(jié) 語(yǔ)

USB 2.0控制器CY7C68013已經(jīng)被廣泛應(yīng)用到許多數(shù)據(jù)傳輸領(lǐng)域,由于USB具有靈活的接口和可編程特性,大大簡(jiǎn)化了外部硬件的設(shè)計(jì),提高了系統(tǒng)可靠性。該設(shè)計(jì)可擴(kuò)展性好,已經(jīng)被應(yīng)用于數(shù)據(jù)傳輸與采集的板卡上,經(jīng)實(shí)際測(cè)試,沒(méi)有出現(xiàn)數(shù)據(jù)的誤碼等錯(cuò)誤,數(shù)據(jù)傳送正確,傳輸速率可達(dá)30 MHz/s以上,滿足設(shè)計(jì)要求。

評(píng)論