基于Verilog的FPGA與USB 2.0高速接口設計

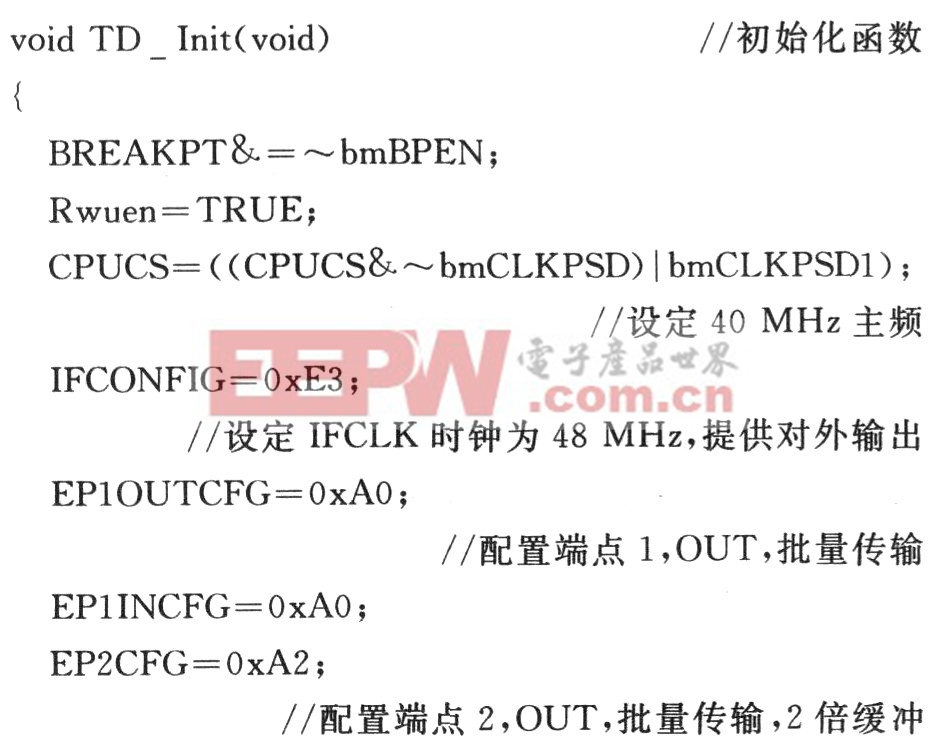

2.2 FPGA控制程序設計

CY7C68013A提供的端口FIFO的讀寫操作,與普通FIFO讀寫操作方式一樣。CY7C68013A為每個端口提供了“空”標志、“滿”標志和“ 可編程級”標志。FPGA檢測這些信號,用于控制讀寫的過程。FPGA在完成這些端口FIFO的操作時,采用Verilog HDL硬件描述語言實現了FIFO的讀寫時序,并在ALTERA公司提供的QuartusⅡ8.O開發工具中綜合編譯并映射到FPGA中運行。

2.2.1 從屬FIFO異步“讀”操作

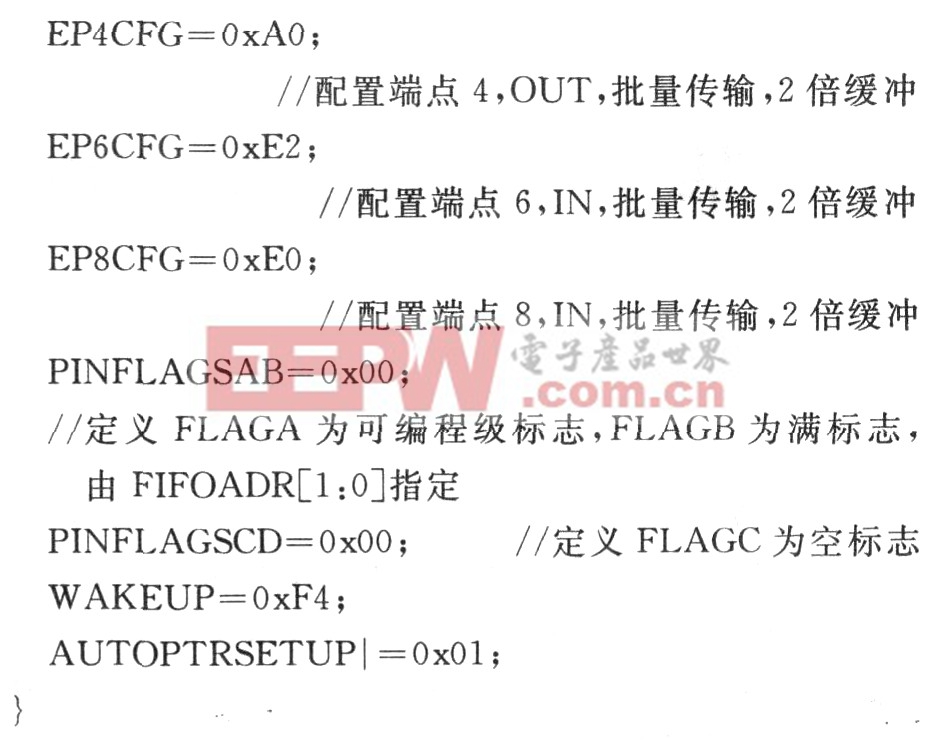

實現異步從屬FIFO“讀”的狀態機如圖3所示。其狀態轉移進程如下:

IDLE:當“寫”事件發生時,轉到狀態1。

狀態1:指向OUT FIFO,激活FIFOADR[1:O],轉向狀態2。

狀態2:激活SLOE,如果FIFO空標志為“假”(FIFO不空),則轉向狀態3;否則停留在狀態2。

狀態3:激活SLOE,SLRD,傳送總線采樣數據;撤銷激活SLRD(指針加1)和SLOE,轉向狀態4。

狀態4:如果有更多的數據要求,則轉向狀態2;否則轉向IDLE。

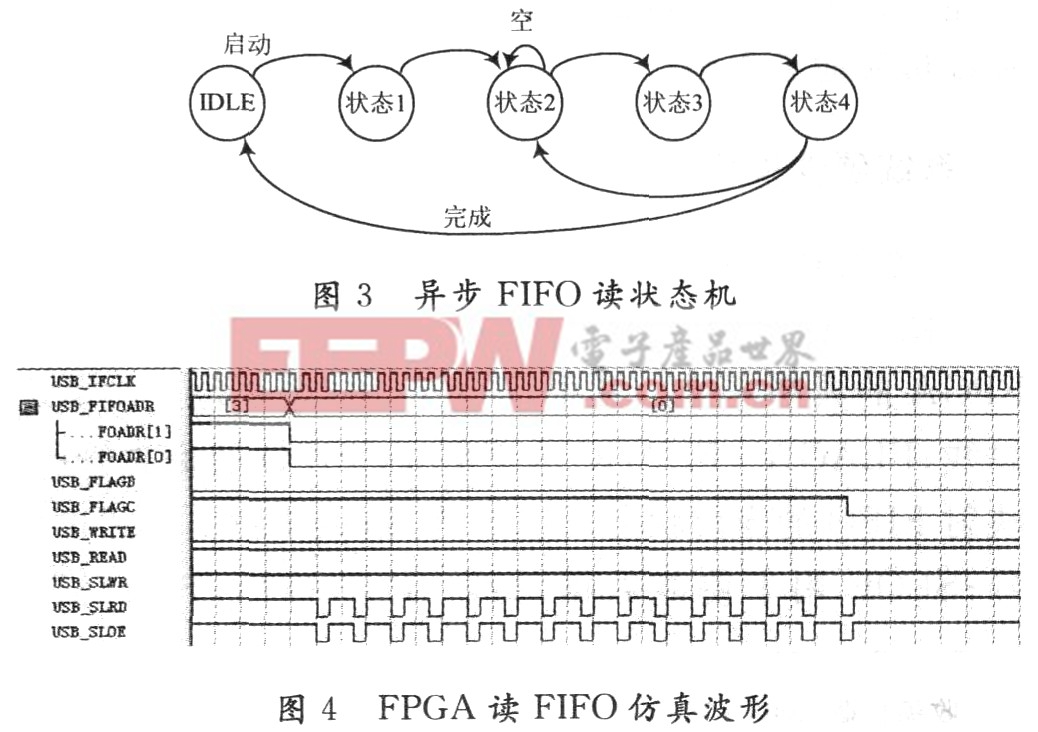

實現以上狀態機的仿真波形如圖4所示。

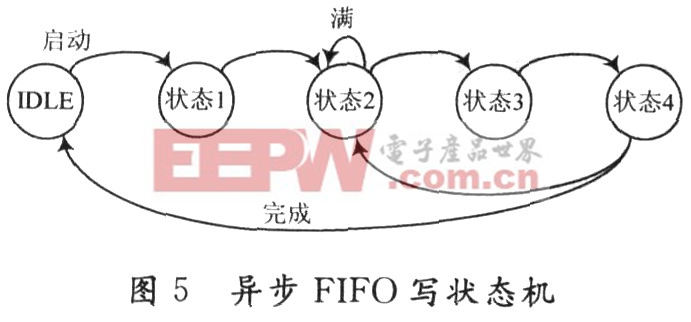

2.2.2 從屬FIFO異步“寫”操作

實現異步從屬FIFO“寫”的狀態機如圖5所示。其狀態轉移進程如下:

評論