基于LEON3處理器和Speed協處理器的復雜SoC設計

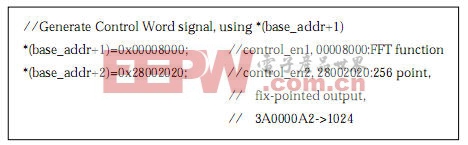

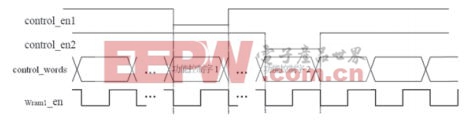

為了使Speed可以順利接收LEON3傳送過來的控制字或DMA傳送過來的原始數據,需要在原有的Speed core模塊頂層添加AHB Slaver協議來接收AHB上傳送的數據,以及產生相應波形的HDL代碼來將C程序的信息生成Speed所能識別的信號波形進入Speed模塊內部,即從圖6中的控制字,轉化成圖7中的時序。

圖6 C語言描述的Speed控制字

圖7 Speed core所需的配置時序

同理于控制字,濾波系數和原始數據的輸入亦需要一定的HDL代碼來實現指令或數據向時序圖的轉化,其本質相當于譯碼,實現起來難度不大,此處就不再累述。Speed處理后數據通過狀態信號(zero_flag)下降沿觸發LEON3的中斷響應,實現向外部存儲器的輸出,此過程和數據輸入類似。

編程、編譯及仿真

用戶在C編程時,只需要按照Speed所需的啟動方式,先設置控制字、再輸入濾波系數、然后啟動DMA輸入原始數據。值得注意的地方是,為了實現Speed的運算與DMA中原始數據輸入同步,需要在C代碼的不同指令間插入一定的延遲指令,此延遲間隔可根據軟硬件的響應速度來計算。

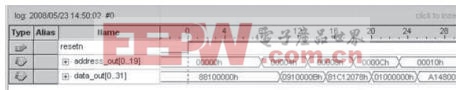

Gaisler Research公司提供完整的LEON3開發套件,包括C代碼編譯器sparc-elf-gcc,大大方便了軟硬件開發和聯合調試。 將LEON3和Speed的SoC硬件HDL描述,及編譯后的二進制指令調入Modelsim進行軟件仿真,再利用FPGA進行硬件仿真,其結果如圖8、9、10所示。

圖8 從C語言控制字產生的配置時序

圖9 觸發中斷響應的zero_flag信號

圖10 在Altera StratixII 2S180中的仿真結果

結語

本項目利用LEON3的高性能、易編程、開源等優點,開發了AHB總線接口和DMA控制器,實現了Speed專用信號處理器的軟件可編程,大大簡化了Speed用戶的開發過程。有待改進之處是,1)當前Speed可處理40bit數據,而Leon3是32bit,沒有最大限度發揮Speed的運算能力;2)如果在LEON3上運行RTEMS (Real Time Executive for Multiprocessor Systems) 操作系統,將進一步方便用戶擴展LEON3的利用價值。

評論