基于CPLD的CIS圖像傳感器驅(qū)動(dòng)電路設(shè)計(jì)

If P_EN ='1' then A1=(others=>'0'); elsif A1_WR'event and A1_WR ='1' then A1=A1+1; end if;

3.5乒乓存儲(chǔ)功能的總線切換

為了提高系統(tǒng)的效率,當(dāng) CPLD在采集數(shù)據(jù)時(shí),微處理器同時(shí)完成前幅圖像數(shù)據(jù)的處理,因此在系統(tǒng)中采用雙緩沖存儲(chǔ)區(qū)[2]。當(dāng) CPLD向 RAM1寫數(shù)據(jù)時(shí),緩沖區(qū) RAM2的總線控制權(quán)交給微處理器。當(dāng)微處理器完成 RAM2中數(shù)據(jù)的處理且 CPLD完成當(dāng)前幅圖像的采集后,總線進(jìn)行切換,使 CPLD將下一幅圖像的數(shù)據(jù)寫入 RAM2,此時(shí) RAM1的總線控制權(quán)切換給微處理器。總線切換由 P_EN的上升沿觸發(fā) EXCH信號(hào)取反。下面的程序是 EXCH信號(hào)在不同情況下,各總線工作狀態(tài)的硬件描述。雙向數(shù)據(jù)總線的 VHDL硬件描述如下。

D=R1D when EXCH='0' and RD='0' else

R2D when EXCH='1' and RD='0' else

ZZZZZZZZ;

R1D=D when EXCH='0' and WR='0' else

D1 when EXCH='1' and A1_WR='0' else

ZZZZZZZZ;

R2D=D1 when EXCH='0' and A1_WR='0'else

D when EXCH='1' and WR= '0' else

ZZZZZZZZ;

地址總線和控制總線切換過程的硬件描述如下。

if EXCH ='0' then

R1A=A;R1_WR=WR;R1_RD=RD;

R1_CE=CS;R2A=A1;R2_WR=A1_WR;

R2_RD='1';R2_CE='0';

else

R1A= A1;R1_WR= A1_WR; R1_RD='1';

R1_CE='0'; R2A= A;R2_WR= WR;本文引用地址:http://www.104case.com/article/191968.htm

R2_RD=RD; R2_CE= CS;

end if;

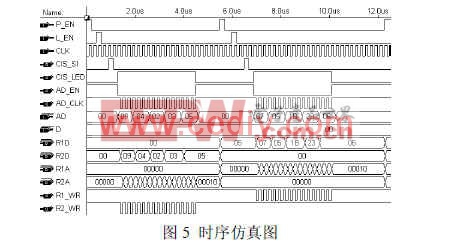

4 結(jié)論圖 5給出了在 Quartus II 6.0中采用 EPM7128QC160型 CPLD對(duì)上述方案的仿真時(shí)序波形圖,仿真結(jié)果與設(shè)計(jì)思想完全吻合。此驅(qū)動(dòng)電路已在紙幣清分設(shè)備中得到較好的應(yīng)用。

本文作者創(chuàng)新點(diǎn):以 CPLD為核心實(shí)現(xiàn) CIS傳感器時(shí)序驅(qū)動(dòng)、A/D轉(zhuǎn)換器控制、雙緩沖區(qū)的乒乓總線切換以及微處理器接口等功能;微處理器不直接控制底層器件,提高了微處理器的效率;采用雙緩沖區(qū)的乒乓工作方式,圖像采集和圖像處理實(shí)現(xiàn)并行工作,提高了圖像處理系統(tǒng)的性能。

評(píng)論