基于ASIC設計的手工綜合研究

隨著專用集成電路(Application Specific Integrat-ed Circuit)設計的迅速發展,將寄存器傳輸級(RTL)描述的手工綜合成門級網表,是IC前端設計中的關鍵技術。在當前IC設計中,通常在行為級功能驗證后,采用軟件進行自動綜合的方式。這種方式雖然縮短了ASIC設計的周期,但是利用軟件綜合的門級電路存在很大的冗余,從而影響到整個芯片的版圖面積和延時。如果采用手工綜合,則會得到最簡的電路結構和最少的線路延時。在總體上,手工邏輯綜合可分為時序邏輯綜合和組合邏輯綜合。

在此,以成功開發的無線發碼遙控編碼芯片為實例,詳細介紹手工綜合RTL級代碼的理論依據和實用方法,重點介紹時序邏輯綜合的實現方法,將時序邏輯綜合的實現方法歸納出各種描述的一般特征,將用戶多種多樣的描述歸整為五種形式,避免了綜合過程中的盲目性,使得整個綜合過程有據可依,從而提高綜合的效率和準確性,并對手工綜合進行深入的研究。

1 組合邏輯綜合

組合邏輯綜合的功能是對組合邏輯函數的描述形式進行一系列轉換和優化,求取實現該邏輯函數性能最佳的組合邏輯結構形式,并生成與邏輯功能描述相等價的優化的邏輯級結構描述。由于行為級描述或寄存器傳輸級描述經轉換后所得到的邏輯級的邏輯函數表示通常都是非優化的表示,因此就需要使用邏輯優化工具對其進行綜合和優化。

組合邏輯綜合的目標通常有:其一是為了在滿足延遲的約束下將面積最小化;其二是為了提高電路的可測試性。

組合邏輯電路設計是數字電路設計的基礎。相對時序邏輯電路而言其綜合過程要簡單,可參考上面的手工綜合步驟,在這里設計了兩個電路對ASIC的手工綜合進行具體研究。

1.1 單增量加法器(4位)

所謂單增量加法器,就是在二進制計算中,行使代碼換算的任務,即二進制計算中若輸出有N值存在,接下來的數值就是N+1,為了把輸出值從N變為N+1就必須做一個電路。若其Verilog HDL描述語言為:

counter_disp=counter_disp+4'd1;

則綜合步驟為:

(1)列出真值表(略);

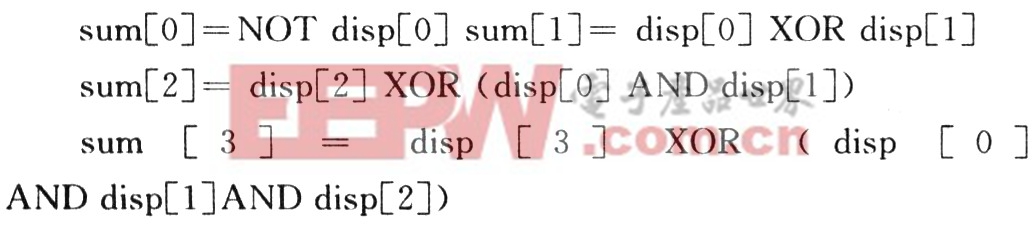

(2)從真值表可以得出其邏輯表達式為:

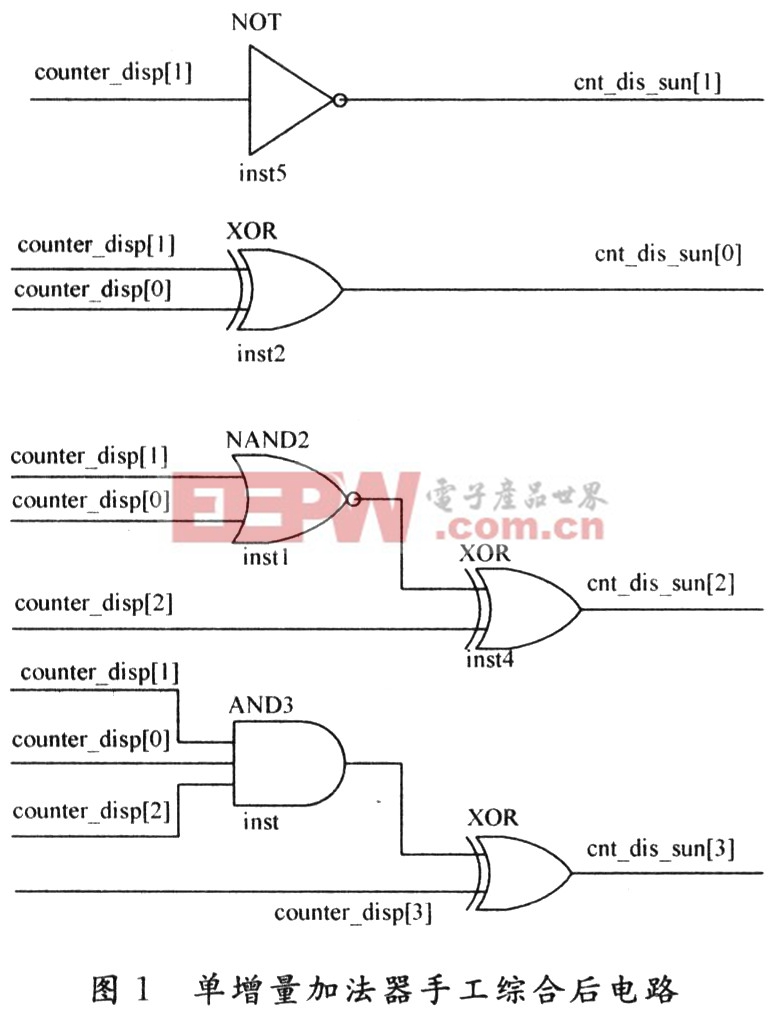

(3)綜合后的電路圖如圖1所示。

評論