基于FPGA的8085A CPU結構分析與實現

1 引 言

微型計算機原理幾乎是所有理工科類大學生的必修課目之一, 其重要性不言而喻。然而大多數教學側重于應用方面, 對計算機的結構及工作原理涉之不深, 因為無法做一個CPU 來演示。這樣學生不能真正了解其性能特點, 掌握內部結構, 在學習匯編語言的時候增加了難度, 影響學習興趣。隨著可編程邏輯器件的廣泛應用, 給數字系統的設計帶來了極大的靈活性, 用戶可以利用現場可編程門陣列FPGA 來開發出一個適合自己的專用CPU, 對微型計算機的原理及結構進行充分理解與研究, 便于將來從事相關ASIC設計, 開發出創新型的產品, 為我國計算機發展做貢獻。

現場可編程門陣列FPGA 門數眾多, 人們可以將合適的IP軟核或其他形式的核作為嵌入式模塊裝在自己的設計中。但通常IP軟核需要門數較多的FPGA 器件支持, 作為學習來說的FPGA 芯片往往資源有限, 需要節約FPGA 的成本與面積; 并且沒必要實現所有功能, 只要做出關鍵部分及重要結構,明白其運行機理, 又能與真實的CPU 緊密相聯即可。實驗箱上采用的FPGA 芯片為A ltera 公司的EPF10K20TC144- 4。這里以Inte l的8085A 為例來說明8位計算機的工作原理。

2 8085A CPU 設計及實現

2. 1 FPGA 芯片及外圍電路簡介

A ltera的FLEX10K 器件是工業界首例嵌入式PLD, 基于可重配置CMOS SRAM 元件。EPF10K20帶有144個LAB (邏輯陣列塊) 和1152 個邏輯單元, 最大I/O數目為189。另外, 芯片中嵌入式陳列塊( EAB)有6個, 其RAM 總位數為12288。

實驗涉及到FPGA 芯片的外圍部分包括控制開關、2* 8鍵盤輸入、6個數碼管輸出、8個輸入端口、8個輸出端口及2個中斷開關等。主要用來增添程序設計的靈活性及形象性, 使其可現場調試, 驗證結果, 避免單純用軟件仿真的不足。外圍電路控制模塊及結構可參見文獻[ 1] 。

現場調試時可以通過控制開關, 手動從鍵盤輸入相應的地址及數據(通過數碼管顯示), 輸錯可以修改; 用寫使能開關給RAM 寫入相應程序。當輸入完所有程序后, 按下運行開關即可執行程序, 在數碼管上顯示地址、數據及最終結果。控制開關用于配合鍵盤通過手動方式輸入程序, 可以形象化的現場編程。在軟件下載后不使用計算機, 通過按鈕、鍵盤就能將程序輸入到RAM 中, 然后運行, 顯示出結果。

2. 2 CPU模塊

2. 2. 1 內部結構

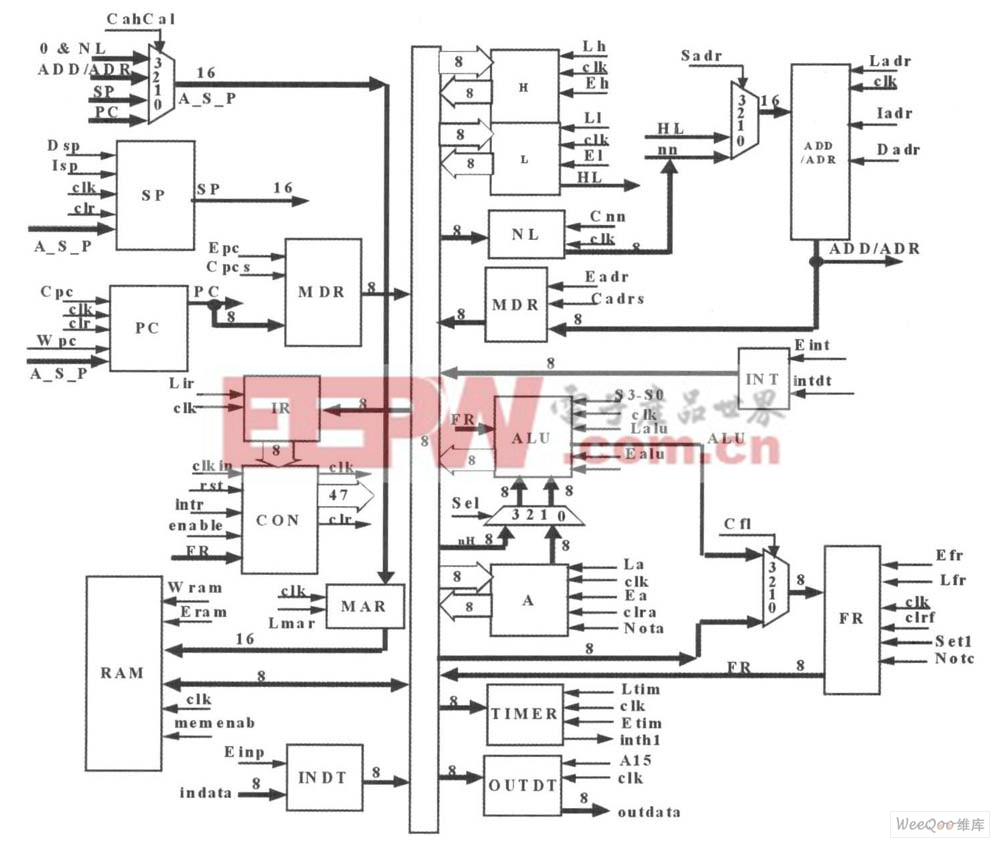

CPU 模塊的內部結構如圖1所示。微型計算機由下面幾個部分組成: 8位通用寄存器H、L, 16位程序計數器( PC ) , 16位堆棧指示器( SP), 一個加1 /減1 地址鎖存器( ADD /ADR ), 8 位NL 寄存器( NL) , 8位中斷時間寄存器( T IMER ) ; 算術邏輯單元(ALU ), 累加器(A ), 標志寄存器( FR ), 數據選擇器( SEL) ; 指令寄存器( IR) , 控制器( CON ) , 4選1多路選擇器(MUX) , 存儲地址寄存器(MAR ) , 8 位數據寄存器(MDR) ; 輸入數據寄存器( INDT ), 輸出數據寄存器( OUTDT )等部分組成。其中標志寄存器有4位, 分別是: 進位位( Cy)、零位( Z)、符號位( S)、奇偶位( P) , 微機通過檢測這些標志位的1位或多位來判斷程序是否需要轉移。

微型計算機CPU 結構圖

圖1 微型計算機CPU 結構圖

圖中字母L為數據載入控制信號, E 為三態輸出選通信號, clk為時鐘信號, c lr為清零信號, W 為數據載入PC信號, Cpc為控制PC 加1信號, S3- S0為控制ALU 進行加減、邏輯運算或移位運算的選擇信號, Iadr、Dadr為加1 /減1地址鎖存器加1減1控制信號, Isp、Dsp為堆棧指示器的加1減1 控制信號, E ram、W ram 為讀寫RAM 控制信號。另外, 累加器(A ) , 標志寄存器( FR )增加了專用的清零信號。

所有的控制、時鐘及清零信號由控制器( CON)模塊給出, 而CON 模塊由外部時鐘clkin、清零信號rst及使能信號enable 控制。存儲地址寄存器(MAR )用來給RAM輸送地址, 從RAM 讀指令和數據, 也可以給RAM寫數據。

評論