基于FPGA的SoC原型驗證的設(shè)計與實現(xiàn)

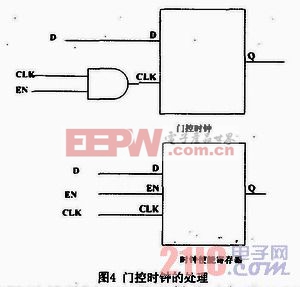

為了減少功耗,SoC設(shè)計中使用了門控時鐘(clockgating),如圖4所示,對于FPGA來說這種門控時鐘容易產(chǎn)生毛刺,導(dǎo)致數(shù)據(jù)不正確,所以在FPGA設(shè)計中要使用時鐘使能寄存器代替門控時鐘。本文引用地址:http://www.104case.com/article/191152.htm

2.2.2 設(shè)計綜合

綜合是將較高級抽象層次的描述轉(zhuǎn)換成較低層次描述,在這里就是把HDL程序轉(zhuǎn)化成標(biāo)準(zhǔn)的門級結(jié)構(gòu)網(wǎng)表。本設(shè)計采用的EDA工具是Sy-nopsys公司的Synplify,將SoC的各個模塊分別進(jìn)行綜合,綜合時要加約束文件和Altera公司的相應(yīng)器件的庫文件,產(chǎn)生一個FPGA網(wǎng)表文件。

2.2.3 等價性檢查

形式驗證(Formal Verification)主要用來在覆蓋所有可能輸入情況下,檢查是否與給定的規(guī)范一致。等價性檢查(equivalence check-ing)是形式驗證中的一部分,它主要是檢查兩個門級網(wǎng)表(gate-level netlisf)之間是否一致,保證網(wǎng)表處理后不會改變電路的功能,或者檢查RTL和門級網(wǎng)表之間是否一致,保證網(wǎng)表能正確地實現(xiàn)RTL代碼所描述的功能,或者檢查RTL間是否一致,保證兩種RTL描述邏輯一致。這種方法主要是用來尋找實現(xiàn)(Implementation Design)中的缺陷,而不是設(shè)計中的缺陷。由于芯片開發(fā)中,設(shè)計代碼將不斷的更改,都需要

更新FPGA的鏡像文件,這樣在頻繁的鏡像制作過程中,可能會因為環(huán)境和設(shè)計的更改引出許多實現(xiàn)過程中的錯誤,而本文為了減少這些錯誤,采用的Synopsys公司的Formality工具,主要用于檢查網(wǎng)標(biāo)和RTL間是否一致,把RTL設(shè)計作為Reference Design,而把網(wǎng)標(biāo)作為Imple-mentation Design,在進(jìn)行等價性檢查時要加入Altera器件綜合過程中需要的相關(guān)庫文件。

2.2.4 設(shè)計整合和布局布線

把多個設(shè)計文件轉(zhuǎn)換合并到一個設(shè)計庫文件中,并把整合后的設(shè)計輸入到Altera公司的QuartuslI工具,將綜合過的網(wǎng)表中的邏輯門映射到FPGA的內(nèi)部資源中,如ALUT等。

布局是指從映射取出定義的邏輯和輸入輸出塊,并把它們分配到FPGA內(nèi)部的物理位置,布線是指利用自動布線軟件使用布線資源選擇路徑試著完成所有的邏輯連接。

2.2.5 時序分析

在設(shè)計實現(xiàn)過程中,在映射后需要對一個設(shè)計的實際功能塊的延時和估計的布線延時進(jìn)行時序分析。而在布局布線后,也要對實際布局布線的功能塊延時和實際布線延時進(jìn)行時序分析。時序分析不僅可以檢查出我們代碼設(shè)計中的時序問題,還可以檢查出由于布局布線產(chǎn)生的時序問題。在本設(shè)計中用Altera公司的TimeQuest來進(jìn)行時序分析,通過對原型設(shè)計增加時序約束,提高了工作主頻和減少了關(guān)鍵路徑的延時。在設(shè)計中經(jīng)常存在時序違約的情況,這時需要查看違約的關(guān)鍵路徑,然后查找原因,進(jìn)行修改后再進(jìn)行時序分析,重復(fù)整個過程直到滿足要求。

2.2.6 鏡像文件的生成和下載配置

QuartusII經(jīng)過整合、布局布線等一系列操作后,最終會生成一個配置FPGA的位流文件(.sof洛式),然后利用QuartusII的Programmer工具,通過USB Blaster下載到FPGA,此時FPGA實現(xiàn)了原SoC設(shè)計的功能,原型驗證環(huán)境搭建完成。

3 FPGA原型驗證測試激勵的設(shè)計

測試程序在FPGA基原型驗證中起至關(guān)重要的作用,現(xiàn)在的SoC設(shè)計很多都采用IP復(fù)用的方式,本文所設(shè)計出的測試程序有可重用性好、功能覆蓋率高和調(diào)試簡易等特點。

測試程序的基本框架如圖5所示,具體模塊的測試程序只需要根據(jù)框架所提供的接口進(jìn)行編寫相應(yīng)的測試程序即可,代碼主要由以下四部分組成:

(1)系統(tǒng)啟動部分。主要包含系統(tǒng)的異常向量表和系統(tǒng)啟動后設(shè)置ARM內(nèi)核的配置程序,如各種模式下的堆棧設(shè)置、開啟或關(guān)閉FIR和IRQ、設(shè)定中斷向量表等,在Boot_gfd.s中提供了跳到測試程序的接口。

(2)模塊測試部分。在此部分根據(jù)各個模塊的功能,編寫相應(yīng)的測試函數(shù),系統(tǒng)在執(zhí)行時會調(diào)用這些函數(shù),完成我們各個模塊的功能測試。

(3)頭文件部分。為了方便代碼的編寫和理解,在tyoedef.h文件中對系統(tǒng)的數(shù)據(jù)類型做了重新定義并包含了部分公用函數(shù)的宏定義。一個SoC系統(tǒng)中擁有大量的寄存器,在本設(shè)計中用Register.h文件來存放這些寄存器地址的宏定義。

評論