基于FPGA的SoC原型驗證的設計與實現

摘要:在SoC開發過程中,基于FPGA的原型驗證是一種有效的驗證方法,它不僅能加快SoC的開發,降低SoC應用系統的開發成本,而且提高了流片的成功率。文章主要描述了基于FPGA的SoC原型驗證的設計與實現,針對FPGA基驗證中存在的問題進行了分析并提出了解決方案。

關鍵詞:現場可編程門陣列;系統級芯片;原型驗證;驗證平臺

0 引言

隨著SoC設計規模的與日俱增,其功能日趨復雜,芯片的驗證階段占據了整個芯片開發的大部分時間。為了縮短驗證時間,在傳統的仿真驗證的基礎上涌現了許多新的驗證手段,如SDV(Software Driven verification)、BFM(Bus Function Model)等,以及基于FPGA的原型驗證技術。

因FPGA工藝及技術的發展,其速度、容量和密度都大大增加,功耗和成本在不斷的降低,使得基于FPGA的原型驗證得到廣泛的應用。基于FPGA的原型驗證可以比軟件仿真速度高出4~6個數量級,而且還可以提高流片成功率,并為軟件開發提供了硬件平臺,加速了軟件的開發速度。

本文主要論述了FPGA基原型驗證的實現方法,并且針對ARM1136為內核的SoC,如何快速而有效地搭建一個原型驗證平臺做了詳細的論述,最后還以UART為例來說明一種簡單、可重用性好、靈活性強的測試程序架構。

1 基于ARM1136的SoC設計

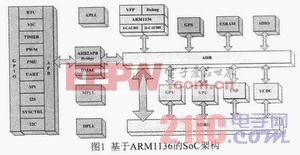

本文驗證的SoC芯片是定位于手持視頻播放設備、衛星導航產品的高性能應用處理器,采用了ARM1136作為內核,ARM11在提供超高性能的同時,還能保證功耗、面積的有效性。

同時在這個架構中還采用了ARM公司的AMBA(Advanced Microcontroller Bus Architecture)總線,它是一組針對基于ARM核的片上系統之間通信而設計的標準協議。在設計中,對于一些處理數據和通訊速度要求較高的設備掛在AHB總線上,而那些對總線性能要求不高的設備掛在APB總線上。

為了能夠提高一些設備間的數據傳輸速度,該設計加入了DMA,其支持存儲器到存儲器、存儲器到外設、外設到存儲的傳輸。

基于ARM11設計的SoC系統構架如圖1所示,這個系統還包括了USB控制器、LCD控制器、圖像處理單元GPU、視頻處理單元VPU、GPS、I2S、通用異步串口UART、同步串口SPI、TIMER、PWM、實時時鐘(RTC)、I2C總線和功耗管理單元(PMU)等。

2 FPGA原型驗證平臺的快速搭建

FPGA的發展為SoC的原型驗證提供了巨大的發揮空間,面對復雜的SoC系統,傳統的一些驗證方法和單一的驗證技術已經不能滿足設計的要求。本文所設計的平臺不僅能加快開發速度,提高流片成功率,而且還具有低錯誤率、快速和簡易的特點,因此特別適合用于RTL代碼更改頻繁的設計中。

評論