基于FPGA的卷積碼編譯碼器

2.3.5 判決與輸出

譯碼深度為10,譯碼的輸出只需將譯碼路徑的最高位中出現較多的一位輸出,當“0”和“1”的個數相等時輸出任意一個。由圖4所示的卡諾圖可得,譯碼輸出的邏輯表達式為:

dataout=(route0 (9) and routel (9)) 0r (route2 (9) and route3 (9))本文引用地址:http://www.104case.com/article/190979.htm

2. 3.6 譯碼初始化

由于剛開始譯碼的第一步和第二步,譯碼路徑并未完全展開,“加-比-選”與后面的步驟略有不同。因此設置一個譯碼步驟計數器step,對譯碼前兩步的“加”進行單獨處理,而不改變“比選”部分。

2.3.7 路徑量度的溢出

由于路徑量度是一直累加的,如果不進行處理則計數器將溢出。設計中發現,各條路徑之間的路徑量度相差不會太大。解決的辦法是:如果有一個路徑量度超過了某一門限,就將所有記錄的路徑量度減一個小量。在實際中,由于(2,1,3)卷積碼每一步譯碼后路徑量度最多增加2,因此為避免溢出,設置門限為8,當超過該門限時各路徑量度都減小2。這樣就可以用很少容量的寄存器保存任意長的路徑量度。

3 仿真結果

仿真在MaxplusII10.2環境下進行,選擇FLEX1OK系列中的EPF10K30RC240-3器件。以下是部分仿真結果。

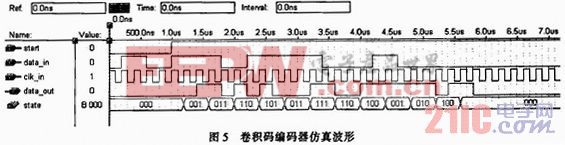

3.1 卷積碼編碼器仿真

卷積碼編碼器的仿真波形如圖5所示。在編碼使能之后輸入序列data_in為110111001000…(每個bit持續2個時鐘周期),編碼輸出序列data_out為110101000110011111101100……(每個bit持續1個時鐘周期),結果與文獻中的例12-1完全一致。

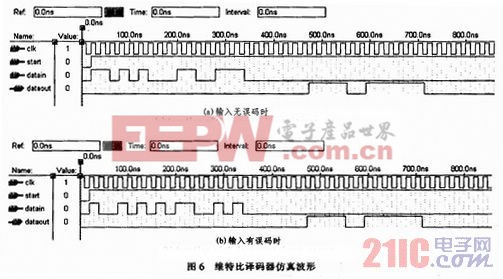

3.2 維特比譯碼器仿真

維特比譯碼器的仿真波形如圖6所示。其中圖(a)為輸入無誤碼時的情形,圖中輸入序列為1101010001100111…,譯碼輸出序列為110111 00…;圖(b)為輸入有誤碼時的情形,圖中假設輸入序列為1001010101100101…(其中黑體的bit為誤碼),則譯碼輸出序列仍為11011100…。

由仿真結果可以看出。用上述方法設計的卷積碼編/譯碼器功能正確,并具有較好的糾錯能力。

4 結論

本文用VHDL語言和FPGA芯片設計并實現了(2,1,3)卷積碼編碼器及維特比譯碼器。仿真結果表明,編/譯碼器的功能正確,達到設計要求。在設計中采用了模塊化結構,維特比譯碼器設計采用了截尾譯碼算法,節省了存儲空間。另外,設計中還較好的解決了譯碼過程中的支路度量計算、路徑量度和譯碼路徑的更新與存儲以及譯碼判決與輸出等關鍵技術問題。

由于卷積碼具有相似的結構和特點,所以文中(2,1,3)卷積碼編/譯碼器的設計思路,對其他形式的卷積碼編/譯碼器也是適用的。

評論