基于FPGA與ARM的遙測數據網絡化采集

摘要:現有的遙測接收機為PCI接口,需安裝在工控機上使用,為實現設備小型化、便攜化,設計實現了小型網絡接口遙測解調模塊,可配合帶有網口的計算機使用。采用FPGA進行遙測數據的幀同步與IRIG—B時碼解調,將接收到的遙測數據添加時碼后發送給ARM處理器中的Linux系統,并編寫Linux 2.6下的FPGA驅動程序,實現FPGA數據的讀取,然后通過網卡以TCP/IP格式發給主機,主機實現數據存儲與顯示。

關鍵詞:FPGA;幀同步;ARM;遙測數據;網絡化;Linux

以太網接口通信速度快,傳輸可靠,使用和配置方便,對于20 Mb/s以下的碼速率,100 Mb/s的網卡可以進行不丟包轉發,采用TCP包格式還可使設備小型化,便于數據的轉發,因此有必要擴展設備的以太網功能。

1 整體模塊設計

1.1 系統設計

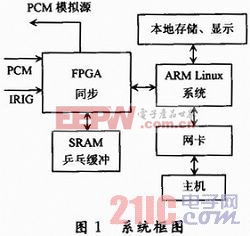

系統設計框圖如圖1所示。其中,采編器或接收機解調輸出的PCM信號及時鐘輸入到FPGA中進行幀同步,IRIG—B碼信息也送到FPGA中進行解調,得到時間信息。數據與時間一起存入SRAM乒乓緩沖區中,達到一定大小后,FPGA向ARM處理器發器中斷,ARM中運行的Linux系統,將數據取走,進行TCP/IP打包,發送給接收計算機。

在設備開始工作前,需要在計算機端進行參數設置,計算機TCP/IP包將參數發送給ARM處理器,由ARM處理器轉發給FPGA。幀同步器的設計中,碼速率為100b/s~10Mb/s,幀長為4~4 096Word,幀同步碼組為4~32,ARM網卡為100Mb/s。

1.2 硬件實現

PCB采用6層結構,相鄰布線層,水平垂直交叉,電路層與電源層單獨分開,提供良好的電磁兼容特性。

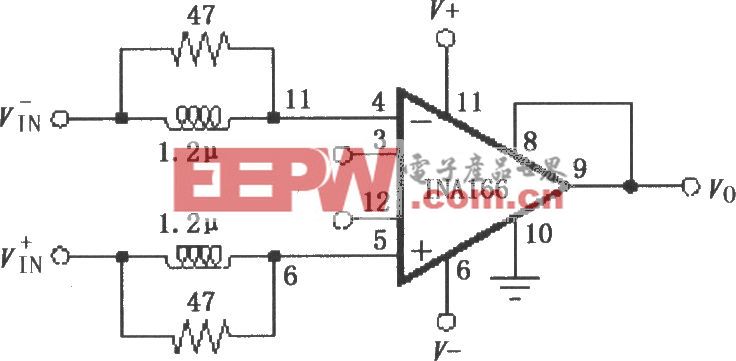

1.2.1 FPGA

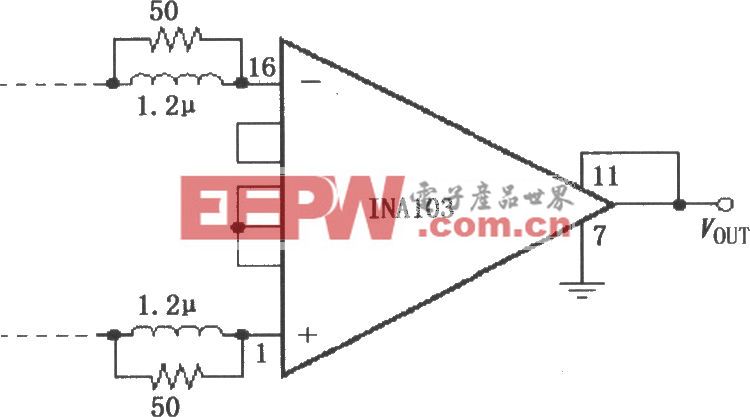

FPGA選擇EP1C12,為實現乒乓緩沖結構,采用SRAM為IS61LV25616。輸入信號使用SMA線纜連接,在傳輸過程中會引入衰減,信號輸入輸出易出現阻抗不匹配的情況,選用AD8556構成射隨器,對輸入信號進行匹配,同時也增大模擬源的輸出能力。

1.2.2 ARM

在此采用S3C2440,內核為ARM920T,最高頻率為400 MHz,帶MMU支持操作系統。內存采用2×32 MB的SDRAM,存儲采用128 MB NAND FLASH,網卡采用DM9000A。

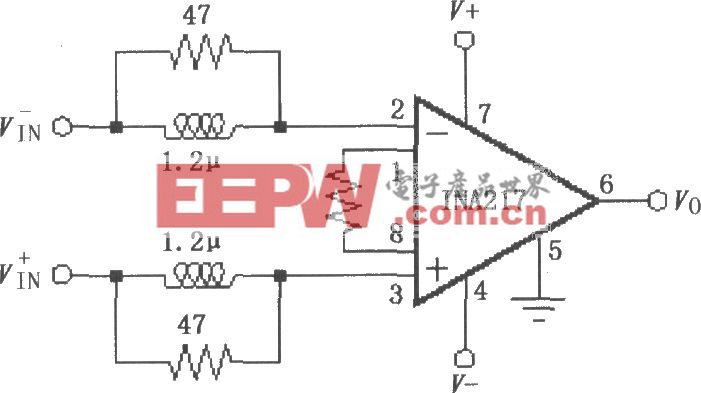

1.2.3 ARM與FPGA的接口連接

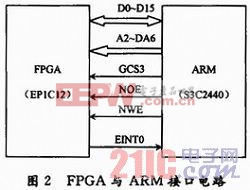

這里采用總線接口,將FPGA作為一個存儲設備掛在ARM的存儲器總線上,如圖2所示。

FPGA在ARM中起始地址為0x18000000,以4 B對齊,占用0x80個地址,地址范圍為0x18000000~Ox1800007C,中斷為EINT0。

在FPGA內部采用讀/寫指針來模擬FIFO,用一個地址來讀取FPGA數據,其余地址用于配置幀同步器與模擬源的參數。

2 幀同步與B碼解調

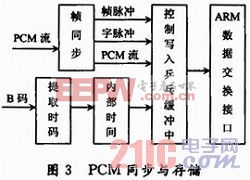

FPGA完成PCM數據的幀同步和解調B碼,寫入到乒乓SRAM緩沖區中,實現如圖3所示。

評論