基于FPGA的卷積碼編譯碼器

2 維特比譯碼器的設計

2.1 維特比譯碼器的原理

卷積碼的譯碼一般采用維特比譯碼。維特比譯碼本質上是對長度為L的二進制序列的最佳譯碼,需要對可能發送的2L個不同的序列的2L條路徑量度進行計算和比較,選取其中量度最小的一條作為幸存路徑。其基礎是基于網格圖的描寫,即對于不同的路徑的量度進行比較,如某一節點上發出的某條路徑已經不可能獲得最大似然函數,那么就放棄這條路徑,并在保存下來的路徑中重新選擇譯碼路徑,一直到最后,復雜度較高。維特比譯碼器實際上對各個可能路徑進行比較,比較原則是計算其路徑的對數似然函數,而計算似然函數就是計算該路徑與接收序列之間的漢明距(量度)。譯碼過程的操作可歸納為“加-比-選”3個部分。

實際的維特比譯碼中,譯碼幾步后可能的路徑便合為一條,因此,不必等全部譯出后再輸出,即譯碼一定長度后便可將已經相同的部分輸出,這樣做可以大量節省譯碼所需路徑的存儲空間。只要保證譯碼深度在5~10倍的約束長度之間就不影響譯碼效果,這就是所謂的“截尾譯碼”。

2.2 結構框圖

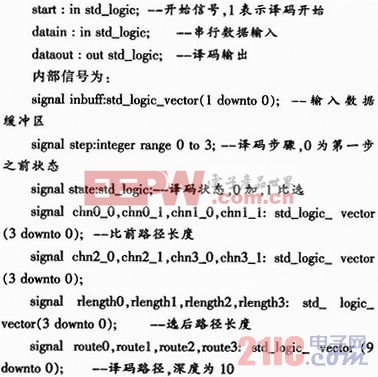

維特比譯碼器的結構框圖如圖2所示。本文引用地址:http://www.104case.com/article/190979.htm

評論