基于FPGA的卷積碼編譯碼器

摘要:基于卷積碼的編譯碼原理,使用VHDL語言和FPGA芯片設計并實現了(2,1,3)卷積碼編譯碼器。其中譯碼器設計采用“截尾”的Vite-rbi譯碼算法,在支路量度計算、路徑量度和譯碼路徑的更新與存儲以及判決與輸出等環節的實現中采取了若干有效措施,節省了存儲空間,提高了設計性能。最后通過仿真驗證了設計的正確性與合理性。

關鍵詞:FPGA;卷積碼;編譯碼器;Viterbi譯碼器:VHDL

由于卷積碼具有較好的糾錯性能,因而在通信系統中被廣泛使用。采用硬件描述語言VerilogHDL或VHDL和FPGA(Field Programmable Gate Array——現場可編程門陣列)進行數字通信系統設計,可在集成度、可靠性和靈活性等方面達到比較滿意的效果。

文獻以生成矩陣G=[101,111]的(2,1,3)卷積碼為例,介紹了卷積碼編碼器的原理和VerilogHDL語言的描述方式;文獻采用VerilogHDL語言,對(2,1,7)卷積碼的Viterbi硬判決譯碼進行了FPGA設計。本文基于卷積碼編/譯碼的基本原理,使用VHDL語言和FPGA芯片設計并實現了(2,1,3)卷積碼編碼器及其相應的Viterbi譯碼器,通過仿真驗證了設計的正確性。

1 (2,1,3)卷積碼編碼器的設計

1.1 (2,1,3)卷積碼編碼器的原理

卷積碼編碼器通常記作(n,k,N),對應于每段k個比特的輸入序列,輸出n個比特;這n個輸出比特不僅與當前的k個輸入比特有關,而且還與以前的(N-1)k個輸入比特有關。(n,k,N)卷積碼編碼器包括:一個由Ⅳ段組成的輸入移位寄存器,每段有k級,共Nk位;一組n個模2加法器;一個由n級組成的輸出移位寄存器。整個編碼過程可以看成是輸入序列與由移位寄存器和模2加法器連接方式所決定的另一個序列的卷積。

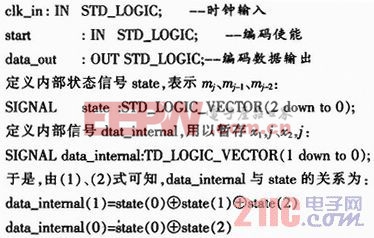

對于(2,1,3)卷積碼編碼器來說,n=2,k=1,N=3,即每輸入1個信息比特時經編碼后產生2個輸出比特,輸出比特不僅與當前的1個輸入比特有關.而且還與以前的2個輸入比特有關。(2,1,3)卷積編碼器框圖如圖1所示。

當編碼使能start為0時不進行編碼,并將狀態state清零;start為1時進行編碼,此時每2個時鐘周期輸入一個新的信息比特,同時狀態信號改變,輸出2位已編碼比特,即每個時鐘周期輸出1位已編碼比特。

評論