SoC系統中實時總線模塊的設計理念與應用

錯誤的處理--最后一根救命稻草

如大家深知,芯片設計是沒有下一次機會的,那么錯誤的處理就成為了“救命的稻草”。假設TDM模塊很久沒有得到總線的控制,出現underrun(速率過低)與overrun(速率過高)情況。要采用隊列中“high-watermark(高水線)”與“low-watermark(低水線)”技術,在隊列接近滿與空狀態發生前提前預警。預警通常反映了芯片系統中的一些設計問題與當時電壓波動、干擾、局部高溫等瞬間問題,這時預警信號通常用最高/次高優先級中斷發生。ARM CPU本身支持高優先級中斷,而我們的隊列長度計算現在要重新計算,加上高優先級處理這一段時間,具體的響應時鐘周期,讀者請查閱相應CPU手冊,這也是評價嵌入式CPU與實時操作系統(RTOS)的一項指標。

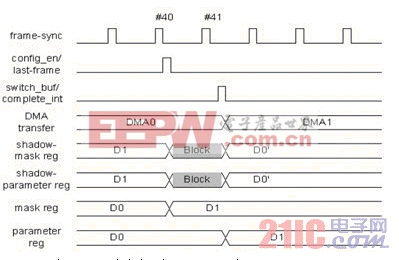

圖4:由TDM模塊實現兩套寄存器的動態切換時序圖。

隊列深度=最長AHB總線獲得間隔×TDM輸入速率+ARM最長中斷響應時間×TDM輸入速率

本文小結

我們在TDM模塊簡要設計中,闡述了結合各種基本技術,如從緩存隊列到DMA到影子寄存器到動態分配到watermark與利用DSP算法特性,AHB總線特性、幀同步特性以及RTOS特性解決非實時與實時交換、CPU效率與資源占用、延時與DMA配置與動態切換的矛盾,追求最優解決方案的過程與設計思路。

本文并沒有給出最初方案的隊列計算公式,是因為要考慮的因素過多,從另一個側面反映了它不是最優方案。好的設計應該是把復雜的需求簡單化、模塊化,當然實際設計中比這種簡化設計要復雜,例如還要解決實時數據傳輸中雙方時鐘不同步等問題。但讀者只要掌握了基本思路與技術,理解應用特性、CPU特性及RTOS特性與算法,就可舉一反三,做出最優的設計。

評論