SoC系統中實時總線模塊的設計理念與應用

這看起來是無解的矛盾,我們可以采用DMA(Direct Memory Access,直接存儲讀寫)技術解決。一般SoC芯片都有外接DDR/SDRAM作為最終的數據與程序緩存,TDM模塊可以直接向DRAM傳輸實時數據,而不用頻繁地中斷CPU,實質上是把片內緩存的需求轉移到了片外(假設總線帶寬足夠),既降低了隊列長度又降低了中斷CPU的頻率,從而解決了這一對矛盾。

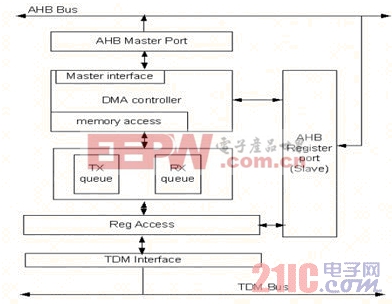

DMA技術實質上也是模塊主動掌握總線主動權,要求采用AHB總線主控模式,最終框架結構會變成圖3所示。

延時與DMA應用的矛盾

細心的讀者會發現DMA的采用增加了處理延時,這不是與我們的原則矛盾嗎?這里牽涉到對嵌入式CPU中音頻處理算法的理解,大多數是音頻壓縮算法,一般都要求有一定的音頻片斷長度以保障壓縮率與減少CPU中RTOS的調度開銷。另外一些音頻處理程序如回響消減DSP算法,經常采用64拍有限濾波器處理大于16ms的回響拖尾。另一些高度壓縮算法(如以有限激勵參數模型為基礎的算法)要求對更長的音頻片斷做處理。所以從算法的角度,SoC系統的音頻處理延時理論下限為多算法處理單元的最大值。我們只要保證DMA的傳輸數據延時小于這個下限就可以了,這樣就充分利用了SoC系統的最小延時,進而計算DMA片斷的長度也有了依據。

回到隊列長度的計算上,我們現在只需要考慮TDM模塊得到AHB總線使用權之間的間隙與TDM數據輸入的速度差的最壞值就可以了。

圖3:最終框架結構圖。

隊列深度=最長AHB總線獲得間隔×TDM輸入速率

AHB總線輪詢(poll)間隙取決于總線上有幾個主控模式模塊與仲裁的優先級策略。一般建議實時模塊享有較高優先級,當然隨之而來的要求是總線申請的頻度不能太高。平衡這一對矛盾的解決辦法超越本文論述的范疇,讀者可以從“固定權重加優先級競爭”的仲裁機制入手來設計AHB總線仲裁器。

動態切換時機與影子寄存器的使用

在實際應用中,我們常常發現幀格式中很多時分信道并沒有音頻數據,這時就要采用時分掩碼來屏蔽這些信道以阻止無效數據占用帶寬。問題是時分信通中是否有數據是動態變化的,動態變化的數據要求時分掩碼參數也要動態分配。但是怎么切換呢?這里采用“影子寄存器”技術,原理是兩套寄存器,一套參數應用于當前幀,另一套應用于下一幀。利用幀同步頭的一個時鐘周期實時切換。而SoC中的CPU只看到一套寄存器地址,同時配置行為本身放寬了實時要求的限制,實時切換由TDM模塊完成,具體圖形見圖4。

評論