設計與驗證復雜SoC中可綜合的模擬及射頻模型

設計用于SoC集成的復雜模擬及射頻模塊是一項艱巨任務。本文介紹的采用基于性能指標規格來優化設計(如PLL或ADC等)的方法,可確保產生可制造性的魯棒性設計。通過這樣的設計,開發者能在保證成本效益和不超預算的前提下,高效、及時地將產品或器件推向市場。

對于當今復雜系統級芯片(SoC)設計,尤其是含有復雜模塊如PLL或ADC等的設計,利用綜合平臺設計者能獲得以下好處:1) 可根據性能規格來創建最優的模塊設計;2) 可對性能與設計余量空間(如芯片面積與速度之間等)之間的折衷進行評估;

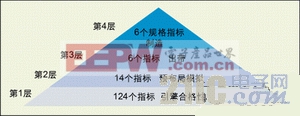

當使用者輸入性能指標規格時,綜合平臺通過將電路公式表示為凸出的優化問題,可同時對器件尺寸及布局布線綜合進行優化。這樣,對設計者的挑戰就只有通過合成來驗證綜合過的設計是否正確,以及能否滿足所有工作條件下的預期性能需求,而不必對每一個實例都進行詳盡的硅驗證。

我們都清楚,在減少芯片體積并使功能最大及功耗最小方面,設計者面臨著巨大的壓力。因此,可靠性余量空間有所減小,這就使得魯棒性模擬及射頻IC的制造成為一項艱巨任務。以下幾種因素需要關注:

1. 電路性能主要取決于晶體管的行為;

制造過程中的很小改動都會導致電路性能的極大變化。在生產期間,改變技術參數可導致電路失敗。針對可制造性設計的目標是以設計為中心,以至于多數被制造的電路能滿足性能規格,同時還能使面積開銷最小化。這就要求不同工藝下都需使用精確的晶體管模型。

2. 由于諸如快速開關數字電路等而產生的基底噪聲耦合,會極大地降低敏感模擬信號的質量;

因此,設計者必須進行仔細的版圖設計以減少器件錯配及寄生效應,這對確保正確的電路行為極為關鍵。不像數字電路,模擬電路要求設計者記住大量性能規格,因此對模擬模塊進行重新設計是一件非常耗時的工作。對于采用0.13微米及以下工藝的設計來說,必須滿足HCE、NBTI及STI應力效應以獲得最佳的模擬及射頻性能。在這些挑戰面前,旨在控制可靠性目標的現有商業工具卻不精確。

如何驗證魯棒性?

通過考慮各種會反向影響制造成品率及性能的因素并將其整合到綜合平臺中,設計者可實現魯棒性設計。

在描述電路行為及性能規格的相同公式中,設計者也可加入多種技術變量。如果邊界設計可行,則意味著只要設計處于可行性范圍內,即無需對每一種新的實例進行驗證。

提高成品率的一項傳統策略是運行多次Monte Carlo模擬,但Monte Carlo分析卻是一項保證成品率最優化的艱苦工作。

Monte Carlo分析可創建一批具有容差元件的電路,并對電路性能進行統計測試。每一種電路都由多個元件(從與用戶定義容差及分布類型相匹配的大批元件中隨機選出)構成。其結果是一條設計約束分布曲線。從此數據可分析出可靠性、成本及制造電路的能力。此概念是在優化程序中使用多次Monte Carlo模擬。

環路的組成為:先由優化器推薦一種候選電路,然后再由評估引擎對每一候選電路的質量進行評估。如此循環反復,直至滿足規格指標為止。此過程被稱為設計中心化方法,實際上只能用于后設計優化。一些商用工具采用SPICE及一個或一組數值搜索引擎。優化者(器)可以是:設計工程師;模擬退火法(Simulated annealing);牛頓法(Newton's method);或任何其他類型的經典優化方法。

不用說,Monte Carlo方法是一種CPU密集型的方法,實際上不可能用于超過數十個晶體管的電路設計中。更重要的是,該方法要求模擬電路設計者及優化專家進行以下工作,即:先由經驗豐富的模擬設計者輸入SPICE架構及測試基準,然后再由優化專家選擇步驟規模、搜索空間及搜索方法。總而言之,Monte Carlo方法要求由專家來對資源進行規劃,而且極為耗時,所有這些因素使得我們需要一種優化成品率的新方法。

凸起優化

模擬及射頻元件(如鎖相環及數據變換器等)的晶體管行為及性能指標,都能用設計變量的多項式來表示。(見圖2)

如果設計者將其設計問題表示為幾何程序,則他能創建一種特殊類型的凸起優化問題。最終解決方案完全獨立于起始點(甚至起始點不可行,且不可行指標能被清楚地檢測到)。設計者能獲得非常有效的整體優化法所帶來的好處,即使是很大的問題,他也能獲得迅速計算出來的結果。如果有這樣的解決方案,則保證程序能獲得收斂。事實上,這是一種能決定全局優化設計的快速綜合方法。

通過改變變量并考慮相關函數中的標記,幾何程序可用公式被重新表示為一種凸起優化問題。在使用幾何程序對電路建模時,設計空間被表現為一種凸起集,而凸起問題則具有特殊的性質:它們的可行集就是凸起。

魯棒性模擬電路創建

正如我們所知,電參數(如晶體管增益等)中的統計變化是由制造工藝中的變化所致,并能影響電路的性能及成品率。通過保證制造及電路設計之間的緊密耦合,綜合平臺可產生出魯棒性設計。

這些工藝變化是由于隨機制造變化所致,且傳統上都被合并到工藝模型中。例如,在制造器件時,摻雜擴散或沉積中的非一致性條件,可導致氧化厚度及擴散深度的改變。氧化厚度及基板、聚合、植入及表面電荷中摻雜水平的變化等,都會對門限電壓值造成影響。照相平版印刷工藝中的分辨率可引起MOS晶體管中的W/L改變。而這些參數改變又會引起電參數(如表面電阻及門限電壓等)發生變化。

例如,用500 MHz統一增益帶寬來將運放限制在一個特定功耗上。為滿足這一約束條件,可在多個工藝階段對設計進行優化,并且還能將電源電壓變化及諸如電阻變化這樣的因素包括在內。表1列出了一些與工藝有關的指標,這些指標作為優化程序的一部分被包括到綜合平臺中。

評論