AES加密算法的高速低功耗ASIC設計

摘 要:本文提出了一個AES加密算法的高速低功耗ASIC設計方案,使用Synopsys設計流程和VeriSilicON 0.18μm CMOS工藝,實現了最高工作頻率410MHz,數據吞吐率5.23Gbps,功耗為58 mW。采用改進算法(T盒算法),將輪變換操作中的不同步驟合并為一組表的查詢,有效降低了關鍵時序路徑的傳輸延遲,并通過動態功耗管理和門控時鐘等低功耗設計方法有效地降低了功耗。

本文引用地址:http://www.104case.com/article/189858.htm1 引言

從1976年美國數據加密標準算法(DES)公布以來,到20世紀末,DES算法或其某些變形基本上主宰了對稱算法的研究與開發進程。隨著密碼分析水平、芯片處理能力和計算技術的不斷進步,DES的安全強度已經難以適應新的安全需要,其實現速度、代碼大小和跨平臺性均難以繼續滿足性的應用需求。因此,AES(高級加密標準)應運而生。作為DES的繼承者,AES自從被接納為標準之日起就已經被工業界、銀行業和行政部門作為事實上的密碼標準。在網絡通信和某些工業控制應用場合,對加密速度的需求成為對AES算法的最關鍵要求,同時功耗成為日漸突出的問題,必須進行低功耗設計。

2 AES加密算法簡介

AES是一個密鑰迭代分組密碼,對加密來說,輸入是一個明文分組和一個密鑰,輸出是一個密文分組。它將分組長度固定為128比特,而且僅支持128、196或256比特的密鑰長度,本文僅對密鑰長度為128比特的情況進行討論。

加密過程包括一個初始密鑰加法,記作AddRoundKey,接著進行9次輪變換(Round),最后再使用一個輪變換(FinalRound)。輪變換由SubBytes、ShiftRows、MixColumns 和AddRoundKey 共4個步驟構成。輪變換及其每一步均作用在中間結果上,將該中間結果稱為狀態,可以形象地表示為一個4*4字節的矩陣。

3 AES的改進算法(T盒算法)

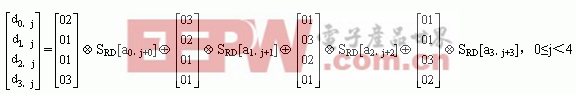

假設加密過程中輪變化的輸入為a,輸出為d,則:

上式中SRD(S盒)由有限域GF(28)中的乘法逆變換和GF(2)中的仿射變換復合而成,符號

代表有限域GF(28)中的加法運算,符號 代表有限域GF(28)中的乘法運算。

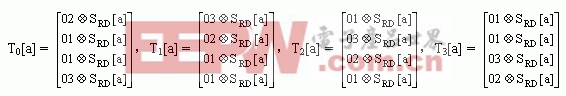

這樣我們可以定義4個表:T0,T1,T2以及T3:

則d簡化為:

該實現方案中T0~T3,每個表都包含了256個雙字,一共占用4KByte的空間。在每次循環迭代中,只要通過4次表查詢和4次異或運算,就能快速地得到一次輪操作中一列的運算結果。改進算法有效降低了關鍵時序路徑的傳輸延遲,能夠明顯的提高ASIC工作頻率。

評論