FCSR原理及其VHDL語言的實現

3時序仿真

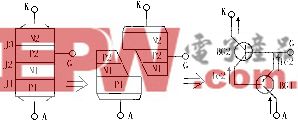

該程序在Lattice公司的ispLEVER軟件環境下編譯、運行和仿真。該FCSR序列發生器可選級數為1~10級,周期范圍為1~2 029。經分析知,當初態為平凡周期狀態(0;0,…,0)和(w -1;1,…,1)時,輸出為全“0”或全“1”。當抽頭置數為“0100000110”,即q9=q3 =q2=1,實際上是一個n=9的l序列發生器;置FCSR初態為(0,0,0,0;0,0, 0,1,1,0,1,0,1,0)時,波形如圖3所示,此時輸出序列的周期T=523。

4需要注意的問題

(1)通過調整SEL及PRN的值并分析輸出序列變化可知,不是任意整數作為連接數都能使F C SR達到最大周期。在工程應用當中,l-序列是最希望得到的。因此在使用FCSR時,應該優先選用那些可以產生l-序列的特殊的連接數,如文獻[1]中提供的一些連接數。

(2)當q為非最大周期連接數時,某些初態會有周期更小的序列輸出。例如當q=17時,ord17(2)=8,即他有最大周期T=8。而實際上除2個平凡狀態外,某些初態會導致輸出T=6的周期序列。在密碼設計中,由于FCSR的初態對應著初始密鑰,這就意味著基于FCSR發生器有弱密鑰。因此,在實際應用中要仔細選擇。

(3)本例中,由于抽頭數最大為9,所以4位進位寄存器即可滿足要求。實際上,當t >2時(t為抽頭數),進位寄存器最小應為log2t。

(4)當加法器采用組合電路實現時,需注意邏輯門延遲影響。在抽頭數較大時,應適當調整電路的時鐘頻率。

5結語

FCSR是一類較新穎的思想,其數學特性目前還不太清晰。因此今后可以從理論和技術實踐兩方面來分析FCSR的隨機特性和應用特點。本軟件在通過時序仿真和適配后,配置La tTIce公司的CPLD器件,輸出序列達到了設計目標。

負離子發生器相關文章:負離子發生器原理

評論