FCSR原理及其VHDL語言的實現

以n=10為例來設計參數可變的FCSR序列發生器。

2.1功能描述及外部引腳

由圖1可知,進位反饋移位寄存器由加法器、進位寄存器和一組(n級)D觸發器組成。加法器實現FCSR的反饋運算;進位寄存器保存前一時刻運算結果除2后的狀態mn-1,并為下一運算提供輸入;n級D觸發器構成移位寄存器,在時鐘控制下實現右移,依次輸出其內部狀態。同時某些觸發器的輸出反饋回來,與進位寄存器的輸出進行運算,和模2反饋至寄存器輸入端,和除2反饋至進位寄存器。

式(1)中qi∈GF(2) ,(i=1,2,…,r-1)在實際電路中為抽頭的連接狀態,決定哪一級輸出反饋至加法器,qi=0表示斷開,qi=1表示連接。

FCSR序列發生器的外部引腳定義如圖2所示。

其中,CLK為時鐘信號;RESET為置數信號;PRN為初態置數端;SEL為抽頭置數端;Q為輸出端。該FCSR序列發生器的特點在于可以通過設定SEL[9…0]的值來改變抽頭數、抽頭位置和發生器的有效級數n(1~10級);當RESET為低電平時,通過設定PR N[9…0]的值改變FCSR的初態,從而可以改變輸出序列周期,分析各種狀態下輸出 序列的變化。

2.2可變參數部分的設計

本設計通過手動或軟件自動設定SEL[9…0]的值來改變抽頭數、抽頭位置和發生器的有效級數3個參數,其中改變最高抽頭位置可使有效長度可變。具體電路中,由SEL[9…0]設定值作為加法器的輸入,輸出結果進行下一步運算,因此需要設計輸入變量較多、延遲時間較短的加法器電路。

這里的求和運算可以等效為計算輸入變量中“1”的個數。對此有多種實現方案,如計數法、邏輯函數法、查表法、求和網絡法等。單純使用一種方法,在輸入變量較多的情況下會有占用資源太多、延遲時間太大或表達式太繁瑣等問題,因此需要綜合使用這些方法。該加法器綜合使用邏輯函數-求和網絡法,由1位累加器和3位串行加法器實現。

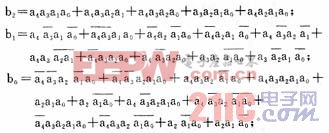

由于n=10,則抽頭數至多為10,可以分2組進行求和。因此首先設計5輸入、3位輸出的累加器。用卡諾圖簡化后,寫邏輯表達式如下:

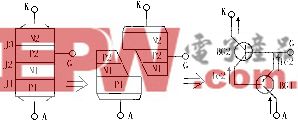

3位串行加法器的設計比較簡單,不再贅述,則10輸入變量、3位輸出的加法器電路原理圖如圖3所示。

這里求和網絡只有1級,不難由此擴充成多級。該電路延遲至多為8級邏輯門的延遲時間,占用資源也較少。

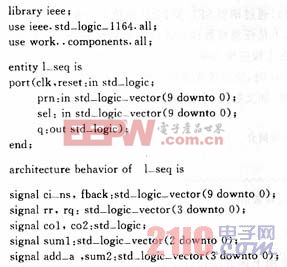

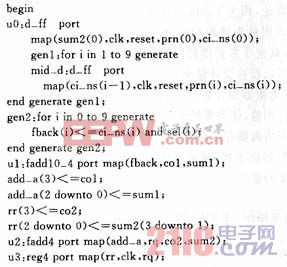

2.3主程序

根據FCSR序列產生的原理,采用VHDL語言的混合描述方式對該邏輯進行硬件描述。主程序l_seq如下:

其中元件例化語句中所引用的元件已經作為組件在compONents.vhd用戶包進行定義,在主程序中調用即可。

負離子發生器相關文章:負離子發生器原理

評論