加速FPGA系統(tǒng)實時調試技術

第4步. 進行測量

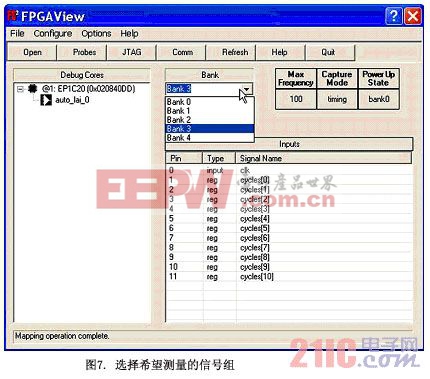

使用Bank(組)列表下拉菜單,選擇想要測量的組。一旦選擇了組,FPGAView會通過JTAG接口與FPGA通信,并配置測試內核,以便選擇希望的組。

FPGAView還將這些通道名稱通過對TLA系列邏輯分析儀的控制進行自動分配,從而可以簡便地理解測量結果。為測量不同的一套內部信號,用戶只需選擇不同的信號組(參見圖7)。全功能TLA系列邏輯分析儀會自動把這些FPGA信號與系統(tǒng)中的其它信號關聯起來(參見圖8)。

在TLA邏輯分析儀中,針對設計人員關心的各種時間信息,提供了業(yè)內獨有的定時參數自動測量功能,通過鼠標簡單的拖放操作,能夠得到周期、頻率、占空比、脈沖寬度、通道/通

道延遲、邊沿計數、周期計數、違規(guī)計數、周期抖動、以及周期間抖動等信息。

小結

通過在FPGA系統(tǒng)和設計與應用階段認真考慮調試需求,可以選擇相應的調試方法,既簡化調試流程,也有助于節(jié)約時間。嵌入式邏輯分析儀和外部邏輯分析儀這兩種方法各有優(yōu)缺點,但FPGAView等新方法進一步提高了外部邏輯分析儀方法的吸引力。能夠快速方便地移動探點,而不需重新匯編設計,同時能夠把內部FPGA信號活動與電路板級信號關聯起來,直接決定著能否滿足產品開發(fā)周期的要求。

評論