加速FPGA系統實時調試技術

選擇合適的FPGA調試方法

上述兩種方法都可以使用,采用哪種方法要視具體情況而定。挑戰在于確定哪種方法更適合您的設計。用戶可以問自己下面的問題:

預計有哪些問題?

如果您認為問題僅限于FPGA內部的功能性問題,那么使用嵌入式邏輯分析儀可以提供要求的所有調試功能。但是,如果預計有更多的調試問題,要求檢驗定時余量、把內部FPGA活動與電路板上的其它活動關聯起來、或要求更強大的觸發功能,那么使用外部邏輯分析儀更適合滿足調試需求。

當FPGA芯片針腳包含超過200M的高速總線,例如集成內存控制器的DDRI、DDRII內存總線,以及集成高速SerDes的高速串行I/O總線,信號完整性測試是保證設計成功的基礎。在本文的后半部分會介紹主流的測試工具和方法。

除狀態數據外,是否需要考察快速定時信息?

外部邏輯分析儀允許以高達125 ps的分辨率(8GS/s采樣)查看FPGA信號詳細的定時關系,這有助于檢驗設計中實際發生的事件,檢驗設計的定時余量。嵌入式邏輯分析儀只能捕獲與FPGA中已有的指定時鐘同步的數據。

需要捕獲多深的數據?

外部邏輯分析儀提供的采集內存更深。一般在嵌入式邏輯分析儀中,最大取樣深度設為128 kb,這一數字受到器件限制。而在外部邏輯分析儀中,可以捕獲最多256Mb樣點。這有助于查看和分析更多的問題及潛在原因,從而縮短調試時間。

設計中更多地受限于針腳還是受限于資源?

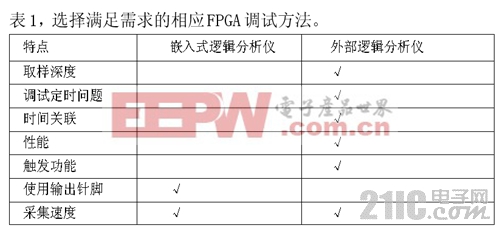

使用嵌入式邏輯分析儀不要求任何額外的輸出針腳,但必須使用內部FPGA資源,實現邏輯分析儀功能。使用外部邏輯分析儀要求使用額外的輸出針腳,但使用內部FPGA資源的需求達到最小(或消除了這種需求)。表1匯總了每種方法的相對優勢。

FPGAViewTM進行FPGA調試

FPGAView概述

外部邏輯分析儀方法有效利用FPGA的處理能力,并根據需要重新對設備配置,把感興趣的內部信號路由到通常很少的針腳上。這是一種非常有用的方法,但它也有一定的局限性:

—— 用戶每次需要查看一套不同的內部信號時,都必需改變設計(在RTL級或使用FPGA編輯器工具),把希望的信號組路由到調試針腳上。這不僅耗費時間,而且如果要求重新匯編設計,那么還會改變設計的定時,可能會隱藏需要解決的問題。

—— 當更改FPGA內部測試信號時,在外部邏輯分析儀上的被測信號名稱需要手工進行更新。

—— 一般來說,調試針腳數量很少,內部信號與調試針腳之間1:1的關系限制著設計查看能

力和洞察力。

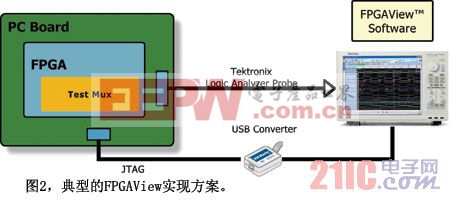

為克服這些局限性,出現了一種新的FPGA調試方法,它不僅提供了外部邏輯分析儀方法的所有優勢,還消除了主要局限性。FPGAView軟件在與泰克TLA系列邏輯分析儀配套使用時,為調試FPGA和周邊硬件電路提供了一個完整的解決方案(參見圖2)。

這種組合可以:

—— 時間關聯的查看FPGA內部活動和外部活動。

—— 迅速改變FPGA內部探點,而無需重新匯編設計。

—— 每個針腳監測多個內部信號。

—— 在TLA邏輯分析儀上自動更新切換的內部信號名稱。

此外,FPGAView可以在一臺設備中處理多個測試內核(適合監測不同的時鐘域),并可以在一個JTAG鏈上處理多臺FPGA設備。

[圖示內容:]

PC Board: PCB電路板

Test Mux: 測試復用器

Tektronix Logic Analyzer Probe: 泰克邏輯分析儀探頭

USB Converter: USB轉換器

FPGAView™ Software: FPGAView™軟件

快速使用FPGAView

可以通過下面幾個簡單的步驟使用FPGAView:

第1步. 在設計中配置和插入相應的測試內核

第2步. 加載測試內核信息

第3步. 建立FPGA針腳與TLA邏輯分析儀通道的對應關系

第4步. 進行測量

評論