加速FPGA系統實時調試技術

下面幾節詳細介紹了每個步驟。

第1步. 插入內核

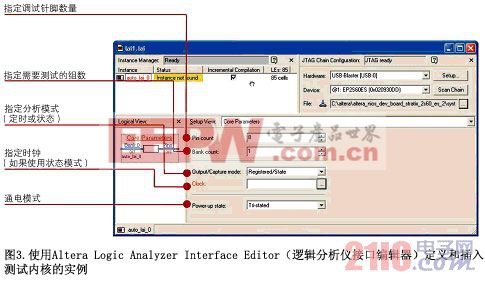

第一步是配置測試內核,把它插入到FPGA設計中。例如,在使用Altera或Xilinx器件時,可以使用FPGA開發工具提供的邏輯分析儀接口編輯器,創建最適合自己需求的測試核(參見圖3)。

[圖示內容:]

Specify number of debug pins: 指定調試針腳數量

Specify Number of Banks: 指定需要測試的組數

Specify Mode: 指定分析模式(定時或狀態)

Specify Clock (if using State Mode): 指定時鐘(如果使用狀態模式)

Power-Up Mode: 通電模式

對大多數測試內核,可以指定下述參數:

Pin Count(針腳數量) :表示希望專用于邏輯分析儀接口的針腳數量。

Bank Count(組數) :表示希望映射到每個針腳上的內部信號數量。

Output/Capture Mode(輸出/捕獲模式):選擇希望執行的采集類型。可以選擇Combination/Timing(組合邏輯/定時模式) 或Registered/State (寄存器/狀態模式)。

Clock(時鐘) :如果用戶選擇了Registered/State(寄存器/狀態)的捕獲模式,這一選項允許選擇測試內核的取樣時鐘。

Power-Up State(通電狀態) :這個參數允許指明指定用于邏輯分析儀接口的針腳的通電狀態。

第2步. 把測試內核信息加載到FPGAView中

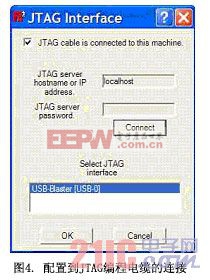

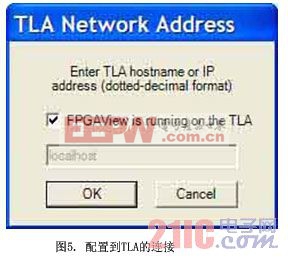

從FPGAView軟件窗口中,可以與JTAG編程電纜建立連接(參見圖4),并且連接到TLA系列邏輯分析儀(TLA邏輯分析儀使用WINDOWS平臺)或PC工作站上(參見圖5)。

在使用ALTERA FPGA芯片時,按Open (打開)工具條按鈕,調出一個文件瀏覽器,選擇Quartus II LAI Editor軟件以前生成的邏輯分析儀接口(.lai)文件。這樣就加載了與LAI核心有關的所有信息,包括每一組的信號數量、組數和信號名稱,另外如果設備中的LAI內核多于一個,那么還包括每個LAI內核的信息。

第3步.

把FPGA針腳映射到邏輯分析儀上

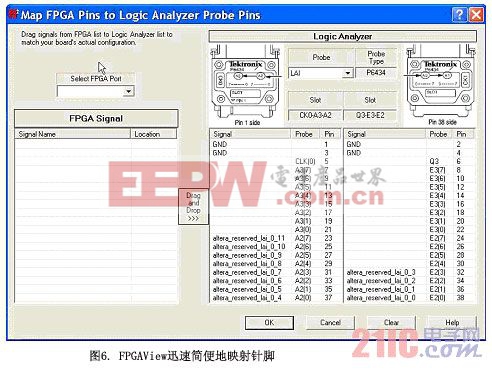

下一步是映射FPGA針腳和TLA邏輯分析儀探頭之間的物理連接。FPGAView可以自動更新邏輯分析儀上顯示的信號名稱,與測試內核當前監測的信號相匹配。

為此,簡單地點擊Probes (探頭)按鈕,將出現一個拖放窗口,把測試內核輸出信號名稱與邏輯分析儀上的相應通道連接起來(參見圖6)。。對某條目標連接,這個通道分配過程只需一次。

評論