加速FPGA系統實時調試技術

摘要:隨著FPGA的設計速度、尺寸和復雜度明顯增長,在整個設計流程中的實時驗證和調試部分成為當前FPGA系統的關鍵部分。獲得FPGA內部信號有限、FPGA封裝和印刷電路板(PCB)電氣噪聲,這一切使得設計調試和檢驗變成設計周期中最困難的流程。本文重點介紹在調試FPGA系統時遇到的問題及有助于提高調試效率的技術,通過邏輯分析儀配合FPGA View軟件快速有效的觀測FPGA內部節點信號。最后提供了FPGA具體的調試過程和方法。

本文引用地址:http://www.104case.com/article/189811.htm引言

隨著FPGA的設計速度、尺寸和復雜度明顯增長,使得整個設計流程中的實時驗證和調試成為當前FPGA系統的關鍵部分。獲得FPGA內部信號有限、FPGA封裝和印刷電路板(PCB)電氣噪聲,這一切使得設計調試和檢驗變成設計周期中最困難的流程。另一方面,幾乎當前所有的像CPU、DSP、ASIC等高速芯片的總線,除了提供高速并行總線接口外,正迅速向高速串行接口的方向發展,FPGA也不例外,每一條物理鏈路的速度從600Mbps到高達10Gbps,高速I/O的測試和驗證更成為傳統專注于FPGA內部邏輯設計的設計人員面臨的巨大挑戰。這些挑戰使設計人員非常容

易會把絕大部分設計周期時間放在調試和檢驗設計上。

為幫助您完成設計調試和檢驗流程,它需要使用新的調試和測試工具,幫助調試設計,同時支持在FPGA上全速運行。

本文重點介紹在調試FPGA系統時遇到的問題及有助于提高調試效率的技術,針對Altera和Xilinx的FPGA調試提供了最新的方法和工具。

FPGA設計流程概述

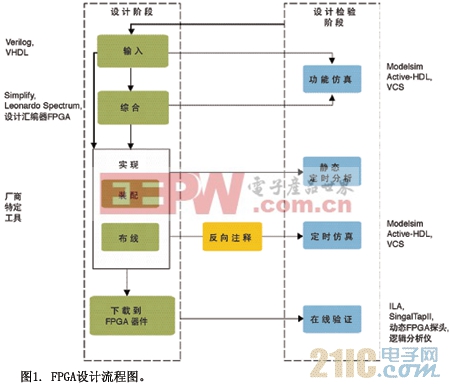

在FPGA系統設計完成前,有兩個不同的階段:設計階段,調試和檢驗階段(參見圖1)。設計階段的主要任務是輸入、仿真和實現。調試和檢驗階段的主要任務是檢驗設計,校正發現的任何錯誤。

[圖示內容:]

Simplify, Leonardo Spectrum, Design Compiler FPGA: Simplify, Leonardo Spectrum, 設計匯編器FPGA

Vendor Specific Tools: 廠商特定工具

Design Phase: 設計階段

Entry: 輸入

Synthesis: 綜合

Implementation: 實現

Place: 裝配

Route: 布線

Download to FPGA Device: 下載到FPGA器件

Back Annotation: 反向注釋

Debug Verification Phase: 設計檢驗階段:

Functional Simulation: 功能仿真

Static Timing Analysis: 靜態定時分析

Timing Simulation: 定時仿真

In-Circuit Verification: 在線驗證

ILA, SingalTap, Dynamic FPGA Probe, Logic Analyzer: ILA, SingalTapII, 動態FPGA探頭, 邏輯分析儀

評論