基于32位微處理器AEMB的SoC系統驗證平臺設計

3.4 中斷控制器與時鐘定時器的配置

中斷控制器主要用于接收外部中斷源的中斷請求,并對中斷請求進行處理后再向CPU發出中斷請求,等待CPU響應中斷并進行處理。在CPU響應中斷的過程中,中斷控制器仍然負責管理外部中斷源的中斷請求,從而實現中斷的嵌套與禁止。在本設計中,中斷控制器的邏輯結構如圖2所示。所采用的中斷控制器主要負責接收片內IP核及片外器件所發出的中斷請求,然后根據一定的優先級與規則將中斷發送給微處理器。微處理器可以通過設置與讀取相應的中斷寄存器來管理查看中斷優先級與中斷狀態。

圖2 終端控制器邏輯結構

時鐘定時器主要是作為操作系統的時鐘滴答定時器,本質上就是一個簡單的計數器。在每個系統時鐘來到時計數器會自動加1,當計數器的值達到設定數值時便產生1次時鐘中斷。PTC是OpenCores組織發布的一個支持Wishbone總線接口的脈沖定時計數器。其不僅可以作為時鐘定時器,還可以通過配置寄存器的設置產生PWM脈沖輸出。本SoC系統中主要是使用PTC的定時器功能。

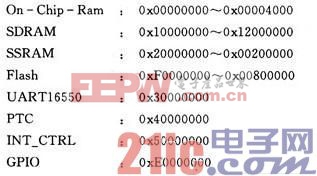

3.5 地址空間的分配

根據DE2-70開發板上各器件的特點與AEMB微處理器的中斷例外向量表及wb_conmax的邏輯實現,系統地址空間分配結果為:

4 SoC系統的FPGA綜合實現

針對DE2-70開發板在進行SoC系統的FPGA綜合時選用CycloneII系列器件EP2C70F896C6。系統時鐘頻率預設為50 MHz,不加額外約束條件下進行綜合,綜合后的邏輯資源占用報告如圖3所示。

圖3 SOC系統FPGA綜合后邏輯資源使用情況

通過時序分析報告可知,該SoC系統在滿足時序的前提下,系統實際運行頻率可達到65.31 MHz。

5 SoC系統驗證平臺軟件支持

考慮到SoC驗證平臺所包含的硬件部件與該平臺的具體應用,系統軟件主要構成如圖4所示。Mini Bootloader負責應用程序從Flash器件向程序運行空間的加載。在DE2-70開發板上,借助于NiosII開發工具與開發板自帶的基于NiosII的SOPC硬件系統,燒寫Flash很方便。系統啟動時可以從Flash開始啟動,完成應用程序的拷貝后再跳轉到主程序運行的存儲器空間。在本系統中,為了使編程更加方便,將拷貝程序放在片上RAM中存儲。系統從片上RAM開始啟動,完成應用程從Flash到SDRAM的拷貝之后,跳轉到SDRAM開始執行應用程序。

圖4 SoC系統軟件支持

AEMB微處理器在指令上與MicroBlaze達到99%的兼容,而后者的應用程序及操作系統的開發已經有非常成熟的范例。操作系統的移植主要是完成對硬件地址空間的修改與操作系統一些底層初始化代碼的編寫。最終在該SoC系統驗證平臺上完成了μC/OS-II的移植工作。

結 語

本文基于32位微處理器AEMB設計了一款SoC系統驗證平臺,給出了SoC系統經過FPGA綜合后的邏輯資源占用情況,以及系統能夠運行的最高時鐘頻率。該平臺已在臺灣友晶公司的DE2-70開發板上完成了FPGA驗證。

評論