專家支招:FPGA與多核CPU使嵌入式設(shè)計(jì)更靈活

隨著嵌入式器件在過去數(shù)十年來的爆炸性成長,使得硬件組件及軟件工具都有顯著的改善。雖然有著這種成長與創(chuàng)新,但傳統(tǒng)嵌入式系統(tǒng)的設(shè)計(jì)方法卻少有進(jìn)步,并逐漸變成一種障礙。有鑒于新標(biāo)準(zhǔn)與協(xié)議的快速發(fā)展,以及對產(chǎn)品上市壓力的日益增加,嵌入式系統(tǒng)設(shè)計(jì)也即將發(fā)生顛覆性的典范改變。

本文引用地址:http://www.104case.com/article/189561.htm隨著硬件技術(shù)及軟件工具的進(jìn)步在加速成長,由整合所帶來的挑戰(zhàn)也開始浮現(xiàn)。如果無法妥善處理這些挑戰(zhàn),將會(huì)使得終端產(chǎn)品變得更加昂貴,并且有礙于讓更多創(chuàng)新設(shè)計(jì)的實(shí)驗(yàn)、成長及上市。

標(biāo)準(zhǔn)的嵌入式架構(gòu)

在一般的計(jì)算市場,標(biāo)準(zhǔn)化已帶來更加穩(wěn)健而耐用的操作系統(tǒng)、更精煉的終端應(yīng)用,及基礎(chǔ)硬件組件的進(jìn)步。我們從其中所學(xué)到的經(jīng)驗(yàn)是,從避免花在客制化硬件架構(gòu)及相關(guān)軟件組件的努力所省下來的時(shí)間,將可獲得更佳的解決方案,這可加快上市的時(shí)間。

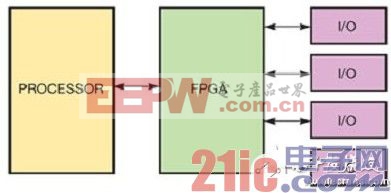

在嵌入式領(lǐng)域,一個(gè)相對應(yīng)的標(biāo)準(zhǔn)架構(gòu)應(yīng)該要具有足夠的靈活性,以容納不同的使用案例,同時(shí)還要能提供一條可以更新的途徑。有鑒于這些限制,在嵌入式領(lǐng)域中的標(biāo)準(zhǔn),最為穩(wěn)健而耐用的架構(gòu)是將一顆微處理器與FPGA相互搭配一起工作,有如一體般(圖A)。這兩者結(jié)合在一起,將可實(shí)現(xiàn)顯著的設(shè)計(jì)靈活性。

圖A:在圖中的標(biāo)準(zhǔn)硬件架構(gòu)中,處理器與FPGA的結(jié)合可實(shí)現(xiàn)靈活性,同時(shí)也讓標(biāo)準(zhǔn)化可以利用較高階的工具,以便在設(shè)計(jì)流程中獲得顯著的效益。處理器可讓現(xiàn)有的碼鏈接庫重復(fù)使用,而FPGA則可讓客制化的算法具有靈活的實(shí)現(xiàn)方式。

FPGA可帶來硬件決定性及可靠性的效益,而不會(huì)有ASIC設(shè)計(jì)突出的成本及缺乏彈性。此外,在FPGA的結(jié)構(gòu)中加載新的邏輯及重新定義鏈接,讓它可以讓工程師實(shí)現(xiàn)不會(huì)過時(shí)的設(shè)計(jì),且有更為穩(wěn)健的更新路徑,而不需要在硬件上進(jìn)行大幅的修改。

在嵌入式系統(tǒng)設(shè)計(jì)中結(jié)合處理器與FPGA的情況,在許多產(chǎn)業(yè)中已是愈來愈普及。嵌入式系統(tǒng)的設(shè)計(jì)開發(fā)工程師都在使用基于多個(gè)處理器及FPGA的設(shè)計(jì)。其中,F(xiàn)PGA用來執(zhí)行精準(zhǔn)且高速的量測,或運(yùn)行時(shí)間關(guān)鍵的算法。同時(shí)處理器則是用來執(zhí)行實(shí)時(shí)的操作系統(tǒng),以處理低頻控制回路及提供連至其他分布式結(jié)點(diǎn)的以太網(wǎng)絡(luò)通訊及促進(jìn)遠(yuǎn)程數(shù)據(jù)的存取、系統(tǒng)的管理及診斷。

高階工具

標(biāo)準(zhǔn)架構(gòu)所帶來的一項(xiàng)關(guān)鍵性效益是,有更多功能強(qiáng)大且優(yōu)化的高階工具可以發(fā)展和使用,以進(jìn)行設(shè)計(jì)。較高階的工具讓某一領(lǐng)域內(nèi)的專家可以更小及更有效率的設(shè)計(jì)團(tuán)隊(duì)深入嵌入式系統(tǒng)設(shè)計(jì)。因此,更小規(guī)模的設(shè)計(jì)團(tuán)隊(duì)便可將更為復(fù)雜的產(chǎn)品推出上市。

效率

以較高階的設(shè)計(jì)工具及語言進(jìn)行應(yīng)用發(fā)展可獲得效率,一般通用的計(jì)算可為此一效率提出證明。毫無意外地,嵌入式市場將開始目睹高階設(shè)計(jì)工具的成長,其中包括 Xilinx AutoESL C-to-Gates高階合成工具、Mentor Graphics Catapult C合成工具及NI LabVIEW最終系統(tǒng)設(shè)計(jì)軟件等。

評(píng)論