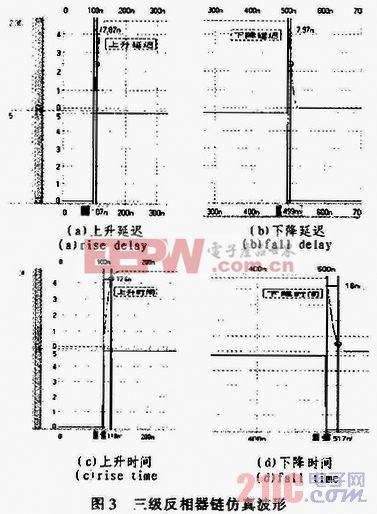

由圖3(a)(b)(c)(d)可知,在輸出緩沖器設計為三級反相器鏈的情況下�����,緩沖器的上升時間tr=17.6 ns���,tf=16 ns,td=15.84 ns�。

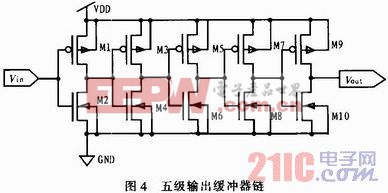

2)把輸出緩沖器設計為五級反相器鏈���,如圖4所示�。

圖4中各個PMOS管和NMOS管的尺寸分別為(取S=2.72)��。

則同樣通過HSPICE仿真軟件��,在0.6μm CSMC 2P2MCMOS工藝庫下的仿真結果為(負載為100 pF電容,1 kΩ電阻)。如圖5(a)(b)(c)(d)所示���,主要考慮仿真結果中的輸出反向器鏈的上升時間tr、下降時間tf、上升延遲和下降延遲td。

電能表相關文章:電能表原理

評論